Архітектура Virtex

1. Банки вводу-виводу

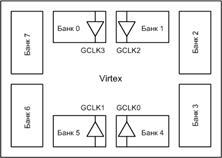

Деякі з описаних вище стандартів вимагають підключення напруги  чи чи  . Ці зовнішні напруги підключаються до контактів мікросхеми, які функціонують групами, названими банками. . Ці зовнішні напруги підключаються до контактів мікросхеми, які функціонують групами, названими банками.

Кожна сторона кристала мікросхеми розділена на два банки. Кожен банк має декілька контактів  , але всі вони повинні бути підключені до однієї і тієї ж напруги. Ця напруга визначається вибраною для даного банка стандартом вихідних сигналів. , але всі вони повинні бути підключені до однієї і тієї ж напруги. Ця напруга визначається вибраною для даного банка стандартом вихідних сигналів.

Стандарти для вихідних сигналів конкретного банку можуть бути різними лише в тому випадку, якщо вони використовують однакове значення напруги  . Сумісні стандарти показані в Табл. 1. GTL і GTL+ присутні скрізь, оскільки їх виходи з відкритим стоком не залежать від значення . Сумісні стандарти показані в Табл. 1. GTL і GTL+ присутні скрізь, оскільки їх виходи з відкритим стоком не залежать від значення  . .

Рисунок 1. – Банки вводу-виводу Virtex

Деякі сигнальні стандарти вимагають подачі відповідних порогових напруг  на вхідні каскади. При цьому визначені БВВ автоматично конфігуруються як входи, відповідні напрузі на вхідні каскади. При цьому визначені БВВ автоматично конфігуруються як входи, відповідні напрузі  . Приблизно один контакт з шести в кожному банку може виконувати цю роль. . Приблизно один контакт з шести в кожному банку може виконувати цю роль.

Таблиця 1. Вихідні сумісні стандарти

|

Сумісні стандарти

|

| 3.3 У |

PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP, GTL, GTL+ |

| 2.5 У |

SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+

|

| 1.5 У |

HSTL I, HSTL III, HSTL IV, GTL, GTL+

|

Контакти  в межах одного банку внутрішньо між собою сполучені, отже, лише одне значення напруги в межах одного банку внутрішньо між собою сполучені, отже, лише одне значення напруги  може бути використано в рамках одного банку. Для правильної роботи всі контакти може бути використано в рамках одного банку. Для правильної роботи всі контакти  одного банку повинні бути приєднані до зовнішнього джерела напруги. одного банку повинні бути приєднані до зовнішнього джерела напруги.

В межах одного банку можна одночасно використовувати входи, які вимагають напруги  і входи, які цього не вимагають. В той же час, лише одне значення напруги і входи, які цього не вимагають. В той же час, лише одне значення напруги  може бути використано в рамках одного банку. Вхідні буфери, які використовують може бути використано в рамках одного банку. Вхідні буфери, які використовують  , не сумісні з сигналами 5-в стандартів. , не сумісні з сигналами 5-в стандартів.

Контакти  і і  для кожного банку приведені в таблицях і діаграмах під конкретний корпус і кристал. На діаграмах також показано, до якого банку відноситься конкретний контакт введення-висновку. для кожного банку приведені в таблицях і діаграмах під конкретний корпус і кристал. На діаграмах також показано, до якого банку відноситься конкретний контакт введення-висновку.

В рамках конкретного типу корпусу мікросхеми число контактів  і і  може мінятися залежно від ємністі кристала. Чим більше кристал по логічній ємністі, тим більше число контактів введення-висновку перетворене в контакти типу може мінятися залежно від ємністі кристала. Чим більше кристал по логічній ємністі, тим більше число контактів введення-висновку перетворене в контакти типу  . Оскільки існує максимальний набір контактів . Оскільки існує максимальний набір контактів  для менших кристалів, є Спроможність проектування друкарської платні, що дозволяє також використовувати на ній і великі кристали з таким же типом корпусу. Всі контакти для менших кристалів, є Спроможність проектування друкарської платні, що дозволяє також використовувати на ній і великі кристали з таким же типом корпусу. Всі контакти  , передбачувані до використовування для великих кристалів, при цьому повинні бути приєднані до напруги , передбачувані до використовування для великих кристалів, при цьому повинні бути приєднані до напруги  і не повинні використовуватися як контакти введення-висновку. і не повинні використовуватися як контакти введення-висновку.

У менших кристалах деякі з контактів  , використовувані у великих кристалах, не сполучені усередині корпусу. Ці не приєднані контакти можуть бути залишені не приєднаними поза мікросхемою або бути підключені до напруги , використовувані у великих кристалах, не сполучені усередині корпусу. Ці не приєднані контакти можуть бути залишені не приєднаними поза мікросхемою або бути підключені до напруги  при необхідності забезпечення сумісності друкарської платні, що розробляється, з великими кристалами. при необхідності забезпечення сумісності друкарської платні, що розробляється, з великими кристалами.

У корпусах типа TQ-144 і PQ-240/HQ-240 всі контакти  сполучені разом усередині мікросхеми і, отже, до всіх з них повинна бути підключене одна і та ж напруга сполучені разом усередині мікросхеми і, отже, до всіх з них повинна бути підключене одна і та ж напруга  . У корпусі CS-144 пари банків, розташовані на одній стороні, внутрішньо сполучені, забезпечуючи, таким чином, Спроможність вибору лише чотирьох можливих значень напруги для . У корпусі CS-144 пари банків, розташовані на одній стороні, внутрішньо сполучені, забезпечуючи, таким чином, Спроможність вибору лише чотирьох можливих значень напруги для  . Контакти . Контакти  залишаються внутрішньо сполученими в рамках кожного з восьми банків і можуть використовуватися, як було описано вище. залишаються внутрішньо сполученими в рамках кожного з восьми банків і можуть використовуватися, як було описано вище.

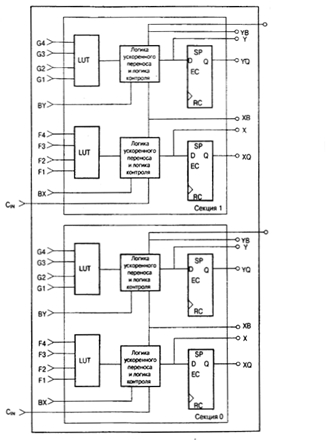

2. Логічний блок, що конфігурується – КЛБ

Базовим елементом КЛБ є логічний комірка – ЛЯ (Logic Cell – LC). ЛЯ складається з 4-входового функціонального генератора, логіки прискореного перенесення і елементу, що запам'ятовує. Вихід кожного функціонального генератора кожного логічного комірці приєднаний до виходу КЛБ і до D-входу тригера. Кожен КЛБ серії Virtex містить чотири логічні комірки, організовані у вигляді двох однакових секцій.

Рисунок 2. – Секційний КЛБ Virtex

На додаток до чотирьох базових логічних комірок, КЛБ серії Virtex містить логіку, яка дозволяє комбінувати ресурси функціональних генераторів для реалізації функцій від п'яти або шести змінних. Таким чином, при оцінці числа еквівалентних системних вентилів для мікросхем сімейства Virtex, кожен КЛБ прирівнюється до 4.5 ЛЯ.

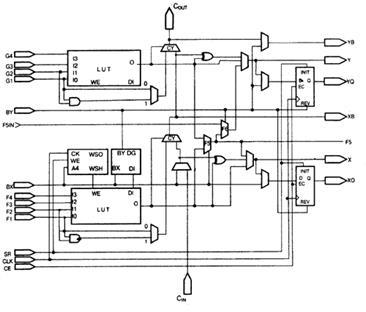

Рисунок 3. – Детальний вид секції Virtex

3.

Таблиця перетворення

Функціональні генератори реалізовані у вигляді 4-входових таблиць перетворення (Look-Up Table – LUT). Окрім використовування як функціональні генератори, кожен LUT-елемент може бути також використаний як синхронне ОЗУ розмірністю 16х1 біт. Більш того, з двох LUT-елементів в рамках однієї секції можна реалізувати синхронне ОЗУ розмірністю 16х2 біта або 32х1 біт, або двохпортове синхронне ОЗУ розмірністю 16х1 біт.

На LUT-елементі мікросхеми Virtex може бути реалізований 16-розрядний сдвиговий регістр, який ідеально підходить для захоплення високошвидкісних або пакетних потоків даних. Цей режим може також використовуватися для запам'ятовування даних в додатках цифрової обробки сигналів.

4. Елементи, що запам'ятовують

Елементи, що запам'ятовують, в кожній секції КЛБ Virtex можуть конфігуруватися як динамічні тригери (чутливі до фронту сигналу) D-типу, або як тригери – клямки, чутливі до рівня сигналу. D-вхід тригера може управлятися або від функціонального генератора в рамках тієї ж секції КЛБ, або безпосередньо від входів даної секції КЛБ, минувши функціональні генератори.

Окрім сигналів синхронізації (Clock) і дозволи синхронізації (Clock Enable – ЦЕ) в кожній секції КЛБ є сигнали синхронної установки (Set) і скидання (Reset). Позначення цих сигналів – SR і BY відповідно.

Сигнал SR переводить елемент, що запам'ятовує, в стан, визначений для нього в конфігураційних даних, а сигнал BY – в протилежний стан. Ці ж сигнали можуть бути використані також як асинхронна передустановка (Preset) і очищення (Clear). Всі сигнали управління можуть бути незалежно проінвертіровани. Вони подаються на обидва тригери в рамках конкретної секції КЛБ.

Додаткова логіка

Додаткова логіка, що входить в кожен КЛБ, представлена двома мультиплексорами: F5 і F6.

На вхід мультиплексора F5 подаються сигнали з виходів функціональних генераторів даної секції КЛБ. Цей вузол може працювати як функціональний генератор, що реалізовує будь-яку 5-входовую функцію, або як мультиплексор 4:1, або як деяка функція від дев'яти вхідних змінних.

Аналогічно, мультиплексор F6 об'єднує виходи всіх чотирьох функціональних генераторів КЛБ, використовуючи один з виходів мультиплексора F5. Це дозволяє реалізувати або будь-яку 6-входовую функцію, або мультиплексор 8:1, або деяку функцію до 19 змінних.

Кожен КЛБ має чотири крізні лінії – по одній на кожен логічний комірка. Ці лінії використовуються як додаткові входи даних, або як додаткові ресурси трасувань, що не витрачають логічні ресурси.

Арифметична логіка

Кожна ЛЯ містить спеціальну логіку прискореного перенесення, яка забезпечує якнайкращу реалізацію на ПЛІС різних арифметичних функцій. КЛБ містить два окремі ланцюги перенесення – по одній на кожну секцію. Розмірність ланцюга перенесення – два біти на КЛБ.

Арифметична логіка включає елемент, що реалізовує функцію виключає АБО, який дозволяє реалізувати однобітовий суматор в одному логічному комірці.

У кожному логічному комірці є елемент, що реалізовує функцію І (AND), який призначений для побудови швидкодійних помножувачів.

Спеціальні траси логіки прискореного перенесення можуть також використовуватися для каскадного включення функціональних генераторів при необхідності створення функцій з великою кількістю вхідних змінних.

Буфери з трьома станами

Кожен КЛБ Virtex містить два буфери з трьома станами, які навантажені на внутрішні шини. Кожен буфер BUFT має незалежний вхід управління з третім станом і незалежний вхідний контакт.

Блокова пам'ять (

Block RAM

)

У FPGA Virtex вбудована особлива блокова пам'ять (Block Select RAM) великої ємністі. Вона створена на додаток до розподіленої пам'яті невеликої ємністі (Select RAM), реалізованої на таблицях перетворення (Look Up Table RAM – LUTRAM).

Блоки пам'яті Block Select RAM+ організовані у вигляді стовпців. Всі пристрої Virtex містять два такі стовпці, поодинці уздовж кожної вертикальної сторони кристала. Ці колонки збільшують повний розмір кристала. Кожен блок пам'яті рівний по висоті чотирьом КЛБ, таким чином, мікросхема Virtex, що має 64 КЛБ по висоті, містить 1–6 блоків пам'яті на колонку і 32 блоки пам'яті в цілому. У Табл. 2 приводяться ємністі блокової пам'яті для різних кристалів Virtex.

Таблиця 2. – Ємність блокової пам'яті

| Кристал Virtex |

Число блоків

|

Загальний об'єм блокової пам'яті [битий] |

|

XCV50

|

8 |

32 768 |

| XCV100 |

10 |

40 960 |

| XCV150 |

12 |

49 152 |

| XCV200 |

14 |

57 344 |

| XCV300 |

16 |

65 536 |

| XCV400 |

20 |

81 920 |

| XCV600 |

24 |

98 304 |

| XCV800 |

28 |

114 688 |

| XCV1000 |

32 |

131 072 |

Кожен блок пам'яті, це повністю синхронне двохпортове ОЗУ з незалежним управлінням для кожного порту. Розмірність шини даних для обох портів може бути конфігурована незалежно, що дозволяє створювати перетворювачі розмірності шини. У Табл. 2 показані можливі співвідношення размерностей шин даних і адреси.

У кристалах Virtex створені спеціальні ресурси трасувань для зв'язку блокової пам'яті з блоками КЛБ і іншими блоками пам'яті.

Рисунок 4. – Блок пам’яті

5. Позначення мікросхем сімейства

Virtex

Спосіб позначення мікросхем сімейства Virtex показаний на рисунку 5.

Рисунок 5 – Визначення МС сімейства Virtex

ПЛІС доцільно застосовувати при розробці оригінальної апаратури, а також для заміни звичайних ІС малому і середньому ступеню інтеграції. При цьому значно зменшуються розміри пристрою, знижується споживана потужність і підвищується надійність.

Найбільш ефективне використовування ПЛІС у виробах, що вимагають нестандартних рішень схемотехніки. У цих випадках ПЛІС навіть середнього ступеня інтеграції (24 виводи) замінює, як правило, до 10–15 звичайних інтегральних мікросхем.

Іншим критерієм використовування ПЛІС є потреба різко скоротити терміни і витрати на проектування, а також підвищити Спроможність модифікації і наладки апаратури. Тому ПЛІС широко застосовується в стендовому устаткуванні, на етапах розробки і виробництва досвідченої партії нових виробів, а також для емуляції схем, що підлягають подальшій реалізації на іншій елементній базі, зокрема БМК.

Окрема область застосування ПЛІС – проектування на їх основі пристроїв для захисту програмного забезпечення і апаратури від несанкціонованого доступу і копіювання. ПЛІС володіють такою технологічною особливістю, як «біт секретності», після програмування якого схема стає недоступною для читання (хоча свої функції ПЛІС, природно, продовжує виконувати). Звичайно застосування однієї-двох ПЛІС середнього ступеня інтеграції виявляється цілком достатньою для надійного захисту інформації.

Найбільш ширше програмовані логічні ІС використовуються в мікропроцесорній і обчислювальній техніці. На їх основі розробляються контролери, адресні дешифратори, логіка обрамлення мікропроцесорів, формувачі управляючих сигналів і ін. На ПЛІС часто виготовляють мікро програмні автомати і інші спеціалізовані пристрої, наприклад, цифрові фільтри, схеми обробки сигналів і зображення, процесори швидкого перетворення функцій Фурье і т.д. У техніці зв'язку

ПЛІС застосовуються в апаратурі ущільнення телефонних сигналів.

Застосування ПЛІС стає актуальним ще і тому, що у розробників часто немає необхідних стандартних мікросхем.

|