Цель и задачи курсового проекта

Тема курсового проекта – «Разработка функциональных узлов (ФУ), выполняющих типовые для цифровых устройств микрооперации».

Целью курсового проектирования являются:

1. Изучение технических характеристик и состава элементной базы современной ЭВМ;

2. Практическое освоение формальных и эвристических приемов выбора оптимального варианта реализации ФУ из множеств возможных;

3. Обучение приемам описания ФУ построения временных диаграмм его работы, ориентировочного расчета быстродействия и потребляемой мощности;

4. Освоение правил оформления функциональных и принципиальных электрических схем;

5. Выработка навыков анализа переходных процессов в ФУ при помощи моделирования на ЭВМ.

Содержание и требования к выполнению курсового проекта.

1. Задание на проектирование ФУ и структурная схема ФУ, соответствующая заданию;

2. Синтез возможных вариантов реализации разрабатываемого узла на уровне функциональных схем с использованием формальных и эвристических приемов проектирования.

3. Сравнительный анализ полученных вариантов и выбор наилучшего варианта по заданному критерию оптимизации;

4. Выбор типа описания используемых серий микросхем:

а) выбор типа системы элементов и конкретной серии с учетом критерия оптимизации ФУ;

б) условные обозначения и технические характеристики конкретных микросхем, используемых в проектируемом узле;

в) описание элементов выбранной серии в целом;

5. Разработка принципиальной электрической схемы ФУ:

а) переход от функциональной к принципиальной электрической схеме; разводка и фильтрация цепей памяти; решение задачи неиспользованных входов микросхемы;

б) временные диаграммы работы ФУ;

в) описание ФУ с использованием временных диаграмм;

6. Расчет быстродействия переходных процессов и потребляемой мощности ФУ на ЭВМ;

7. Заключение и выводы по проделанной работе;

8. Перечень использованной литературы;

9. Приложение. Схема электрическая принципиальная и перечень элементов.

Задание на курсовое проектирование.

Индекс задания состоит из 4 позиций. Индекс моего варианта равен 2.1.5.3. Эти числа указывают на критерий оптимизации, номер задания, номер таблицы, номер варианта в таблице.

Критерий оптимизации:

Максимум быстродействия.

Задание:

Разработать распределитель тактовых импульсов, формирующий на выходах Z 1

и Z2

из N входных импульсов (от ГТИ), последовательности, указанные в таблице 1. Реализация на основе сдвигового регистра, двоичного счетчика.

Таблица 1. (вариант в таблице):

| Вариант |

№ |

Номера импульсов, проходящих на выходы распределителя |

| Режим 1 |

Режим 2 |

Режим 3 |

Режим 4 |

| 3 |

20 |

1,5,6,7,10 |

2,6,7,8,11,12 |

3,7,8,9,12,13 |

4,8,9,10,13,14 |

Для курсового проектирования я взял 2 режима: режим 1, режим 3.

Синтез ФУ.

Таблица переходов:

| № |

Х1 |

Х2 |

Х3 |

Х4 |

1 |

2 |

| 0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

0 |

1 |

1 |

| 2 |

0 |

0 |

1 |

0 |

| 3 |

0 |

0 |

1 |

1 |

1 |

| 4 |

0 |

1 |

0 |

0 |

| 5 |

0 |

1 |

0 |

1 |

1 |

| 6 |

0 |

1 |

1 |

0 |

1 |

| 7 |

0 |

1 |

1 |

1 |

1 |

1 |

| 8 |

1 |

0 |

0 |

0 |

1 |

| 9 |

1 |

0 |

0 |

1 |

1 |

| 10 |

1 |

0 |

1 |

0 |

1 |

| 11 |

1 |

0 |

1 |

1 |

| 12 |

1 |

1 |

0 |

0 |

1 |

| 13 |

1 |

1 |

0 |

1 |

1 |

| 14 |

1 |

1 |

1 |

0 |

| 15 |

1 |

1 |

1 |

1 |

Минимизация (по карте Карно):

1.

Х1х2

Х3х4

|

00 |

01 |

11 |

10 |

| 00 |

| 01 |

1 |

1 |

| 11 |

1 |

| 10 |

1 |

1 |

Z1

=  x4

V x4

V  x2

x3

V x1 x2

x3

V x1

x3 x3

2.

Х1х2

Х3х4

|

00 |

01 |

11 |

10 |

| 00 |

1 |

1 |

| 01 |

1 |

1 |

| 11 |

1 |

1 |

| 10 |

Z2

=x1

V V  x3

x4 x3

x4

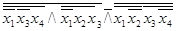

Переход в базис И-НЕ:

Z1

=  x4

V x4

V  x2

x3

V x1 x2

x3

V x1

x3 x3

= =  ; Z2

= x1 ; Z2

= x1

V V

x3

x4

= x3

x4

=

Выбор типа описания используемых серий микросхем

Перспективными, часто используемыми системами, имеющими широкий спектр СИС, являются системы типов ТТЛ, ТТЛШ, ЭСЛ, КМОП. Так как по критерии оптимизации мне достался максимум быстродействия, то я выбрал систему типа ЭСЛ (эмиттерно-связанная логика). Цифровые микросхемы ЭСЛ имеют наибольшее быстродействие, но потребляют значительную мощность. В настоящее время широко используются серии 100, 500, 1500, отличающимися друг от друга типом корпуса и количеством СИС в серии. Особенность ЭСЛ в том, что схема логического элемента строится на основе интегрального дифференциального усилителя (ДУ), транзисторы которого могут переключать ток, но при этом никогда не попадают в режим насыщения.

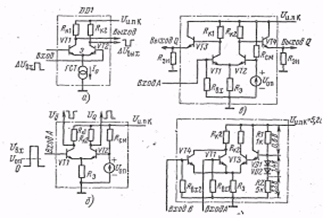

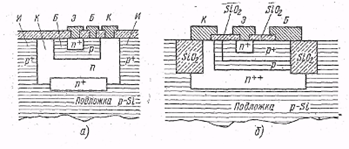

Рис. 1.1. Исходные схемы для элемента ЭСЛ:

На рис. 1.1, а показана основа логического элемента DD1 - переключатель тока. Если входным сигналом открыть транзистор VT, через него потечет весь ток, вытекающий из общей точки эмиттеров - Э. На коллекторе транзистора VT1 окажется напряжение низкого уровня. В этот момент транзистор VT2 тока не имеет, он вынужденно находится в состоянии отсечки. На его коллекторе отсутствует напряжение высокого уровня. Наличие генератора стабильного тока (ГСТ) принципиально - с его помощью строго фиксируются выходные логические уровни.

На рис. 1.1,б показан простейший одновходовой элемент ЭСЛ. Новым в развитии элемента DD1 (рис. 1.1, а) здесь является источник опорного напряжения Uon. Это напряжение фиксирует порог срабатывания переключателя тока. Тем самым дифференциальный усилитель превращается в логический элемент. У него теперь два состояния выходов, которые переключаются лишь при условии: Uвх>Uon. Однако при проектировании ЭСЛ ставилась задача: получить сверхскоростную логику. На схеме (рис. 1.1,б) этого достичь нельзя, так как выходное сопротивление выходов Q и Q с инверсией велико, оно приближается к номиналу Rk. Для снижения выходного сопротивления к коллекторным выходам подключаются эмиттерные повторители-транзисторы VT3 и VT4, работающие в линейном режиме (рис. 1.1, в). Теперь выходное сопротивление эмиттерного выхода принципиально уменьшается.

где (В+1)-коэффициент усиления транзистора - эмиттерного повторителя по току. Эмиттерные выходы чаще делаются «открытыми», чтобы можно было их соединять в элементы «монтажное ИЛИ». Кроме того, внутренние нагрузочные резисторы рассеивают большую мощность, чем сильно ухудшают тепловой баланс корпуса ЭСЛ. Во многих случаях не обязательно отбирать от повторителей VT3-VT4 максимальный ток. Сопротивление внешнего нагрузочного резистора Rн можно выбрать самостоятельно в широких пределах, например от 300 Ом до 30 кОм.

На рис. 1.1, г показан следующий шаг развития схемотехники ЭСЛ: для получения нескольких логических входов следует использовать один пороговый транзистор (в схеме он составной: VT3-VT2) и несколько параллельно соединенных входных транзисторов. В данном случае логическую функцию входов A и B реализуют транзисторы VT4 и VT1. В современных ЭСЛ логические входы снабжаются внутренними резисторами. Такой резистор, во-первых, позволяет оставлять неиспользуемые логические входы свободными, неприсоединенными; во-вторых, эти резисторы служат предыдущим элементам ЭСЛ нагрузками для их выходных эмиттерных повторителей. В правой части схемы (рис. 1.1, г) показан простейший источник порогового напряжения Uon (резисторы R1, R2 и диоды VD1, VD2), который вырабатывает опорное напряжение 4,6 B, он снабжен эмиттерным повторителем VT3 для увеличения нагрузочной способности.

Отметим дальнейшую принципиальную особенность микросхем ЭСЛ: они питаются отрицательным напряжением – -Uи.п. (т.е. - напряжение подается от эмиттеров), причем коллекторные цепи заземляются. Этим способом повышается помехоустойчивость ЭСЛ.

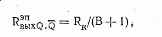

Рис. 1.2. Способы подачи питания на ЭСЛ: а - с заземленными эмиттерами; б - с нулевой коллекторной шиной; в - с раздельными коллекторными выводами

На рис. 1.2, а показана передача сигнала Uc от эмиттерного повторителя VT3 из элемента-источника DD1 (ЛЭЙ) на базовый вход транзистора VT1 в логическом элементе-приемнике DD2 (ЛЭП). Видно, что большой ток потребления Iпот, протекающий по относительно тонкому проводнику коллекторного питания Uи.n.к, имеющему определенное погонное сопротивление R, даст напряжение помехи Un, которое в сумме с сигналом U поступит на вход А2 элемента DD2. Из этого обстоятельства следуют два вывода: во-первых, коллекторная шина питания делается большого сечения и заземляется (дается нуль потенциала, см. рис. 1.2,б); во-вторых, разъединяются коллекторные цепи переключателя тока и эмиттерных повторителей (рис. 1.2, в). Корпус ЭСЛ имеет, таким образом, два вывода коллекторного питания Uи.п. к1 и Uи.п. к2 и один вывод эмиттерного -Uи.п.э = -5,2 В.

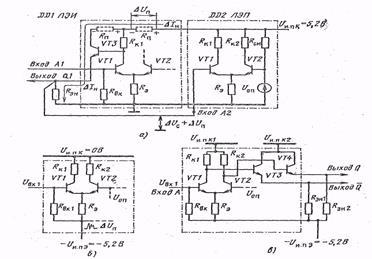

Рис. 1.3. Логический элемент ЭСЛ серии К500: а - принципиальная схема; б - включение; в - схема для снятия переключательных характеристик; г - переключательные характеристики для выходов Q и Q с инверсией; д - временная диаграмма

К помехам, возникающим в шине эмиттерного питания -Uи.п.э, переключатель тока - дифференциальный усилитель менее чувствителен, так как в эмиттерной цепи присутствует генератор стабильного тока, который фиксирует ток, не позволяет ему изменяться, если меняется напряжение источника эмиттерного питания -Uи.п. э (что равноценно помехе). Чем выше качество схемы ГСТ, тем значительнее ДУ ослабляет эмиттерный синфазный сигнал помехи. Желательно, чтобы ток ГСТ не зависел как от пульсаций по шине, так и от изменений температуры. Учитывая вышеизложенную последовательность схемотехнического развития, нетрудно проанализировать полную схему элемента ЭСЛ серии К500 (рис. 1.3, а). На рис. 1.3,б показано включение этого элемента, причем внешние резисторы нагрузки Rн следует присоединять, если данный элемент работает как оконечный. Таким образом, все логические уровни ЭСЛ имеют место в отрицательной области потенциалов («под землей»). Такие логические уровни непосредственно не совместимы со схемами ТТЛ и КМОП, что считается большим недостатком ЭСЛ. Оба коллекторных вывода Uи.п. к1 и Uи.п. к2 присоединяются к нулевой шине (или поверхности) печатной платы. На рис. 1.3, в показана схема, позволяющая снять зависимости выходных напряжений UQ и UQ с инверсией изменения входного напряжения Uвх, которое будем изменять с помощью потенциометра R1. Полученная зависимость представлена на рис. 1.3, г. Видно, что амплитуда, выходных импульсов микросхем ЭСЛ (см. также осциллограмму, рис. 1.3, д): примерно равна 0,9 В.

Рис. 1.4. Поперечные сечения интегральных транзисторов:

На рис. 1.4, а показано поперечное сечение биполярного транзистора с p-n-изоляцией, на котором строились в 70-х годах, как аналоговые микросхемы, так и цифровые ЭСЛ. Такие транзисторы имели частоту единичного усиления f=1,5 ГГц. Плотность упаковки получалась: 10 элементов на кв. мм. Следует отметить, что первые серии ЭСЛ появились еще в середине 60-х годов. В связи с чрезмерно удельной рассеиваемой мощностью этих наносекундных микросхем, многие их варианты тогда имели: массивную гибридную конструкцию. В последующее двадцатилетие широкое распространение как прототипы получили последовательно сменявшие друг друга серии полупроводниковых ЭСЛ фирмы Motorola (например, MECL 100, MECL 1000, MECL 10000, MECL 2500). В ходе развития не только улучшались параметры, но и совершенствовалась схемотехника как собственно элемента, так и функциональных узлов, входящих в серии. Логический элемент серии MECL 10000 (иногда ее обозначают MECL 10К) соответствует схеме рис. 3.3, а.

Серия MECL 100000 (или, кратко: MECL100K) превосходит по быстродействию микросхемы перспективных серий ТТЛШ. На рис. 1.4, б доказан эскиз сечения биполярного транзистора, разработанного для этих субнаносекундных микросхем ЭСЛ. Здесь p-n-изоляция заменена диэлектрической Si02, поэтому транзисторы имеют f=4,5 ГГц, что обеспечивает время задержки=0,75 нс. За счет существенно, меньшей площади интегрального транзистора плотность упаковки повышается до 20 элементов на квадратный миллиметр поверхности, хотя число транзисторов в элементе ЭСЛ стало почти в два раз больше. На таких транзисторах строятся БИС ЭСЛ и матрицы памяти.

Серия MECL 100000 (или, кратко: MECL100K) превосходит по быстродействию микросхемы перспективных серий ТТЛШ. На рис. 1.4, б доказан эскиз сечения биполярного транзистора, разработанного для этих субнаносекундных микросхем ЭСЛ. Здесь p-n-изоляция заменена диэлектрической Si02, поэтому транзисторы имеют f=4,5 ГГц, что обеспечивает время задержки=0,75 нс. За счет существенно, меньшей площади интегрального транзистора плотность упаковки повышается до 20 элементов на квадратный миллиметр поверхности, хотя число транзисторов в элементе ЭСЛ стало почти в два раз больше. На таких транзисторах строятся БИС ЭСЛ и матрицы памяти.

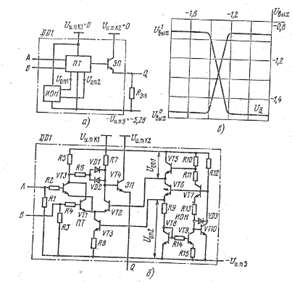

Рис. 1.5. Схемотехника субманосекундной ЭСЛ: а - структурная схема логического элемента; б - схема переключателя тока ПТ, эмиттерного повторителя ЭП и источника опорного напряжения ИОН; в - переключательные характеристики по выходам Q и Q с инверсией

Логический элемент серии MECL 100K имеет диодную цепь термокомпенсации логических уровней, а также усовершенствованный источник опорных напряжений, делающий логические уровни независимыми от больших колебаний питающих напряжений, а также помех по цепи питания. На рис. 1.5, а показана функциональная схема элемента серии MECL 100K, которая содержит три части: переключатель тока ПТ и эмиттерный повторитель ЭП, а также источник опорного напряжения ИОН. Полная принципиальная схема этого элемента приведена на рис. 1.5, б. Эмиттерный повторитель VT4 можно нагрузить на резистор сопротивлением 50 Ом, подключив его вывод к потенциалу - 2В. Предельный ток нагрузки ЭП может достигать 55 мА. Отметим, что все измерения для ЭСЛ следует проводить при установившемся температурном режиме, причем плату с микросхемами следует обдувать (скорость потока 2,5 м/с). Номинальное напряжение питания для серии MECL 100К несколько уменьшено (-Uи.п. э=-4,5 В), однако логические уровни непосредственно совместимы с предыдущей логикой (см. рис. 3,5, в). Благодаря ИОН логические уровни не изменяются, если напряжение питания будет находиться в пределах -4,2 В<-Uи.п. э<-5,7 В. Статическая потребляемая мощность для субнаносекундного элемента Рпот= 40 мВт. Аналогичные параметры имеют микросхемы ЭСЛ серии К1500.

На рис. 1.6 показана диаграмма пределов переключательных характеристик ЭСЛ серий К500 и К1500. В табл. 1.1 даны цифровые значения соответствующих координат входных и выходных напряжений. На диаграмме, построенной для каждой серии, типовые характеристики расположены внутри заштрихованного контура. Следует учесть, что данные столбца для микросхем серии К1500 не зависят от температуры и питающих напряжений. Для микросхем серии К500 приведены значения при 25 °С. При температуре - 30 °С все напряжения возрастают на 5...10 %, а при температуре +85 °С снижаются на такую же величину.

Рис. 1.6. Диаграмма пределов переключательных характеристик элементов серии К1500

Таблица 1.1. Входные и выходные уровни для элементов ЭСЛ

| Обозначение уровня напряжения (см. рис. 1.6) |

Серия |

| К500 |

К1500 |

| Входной, высокий, максимальный Uвх_ max, мВ |

-810 |

-880 |

| Входной, высокий, минимальный Uвх_ min, мВ |

-1105 |

-1165 |

| Входной, низкий, максимальный Uвх_н_мах, мВ |

-1475 |

-1475 |

| Входной, низкий, минимальный Uвх_н_min мВ |

-1850 |

- 1810 |

| Выходной, высокий, максимальный Uвых_в_maх, мВ |

-810 |

-880 |

| Выходной, высокий, минимальный Uвых_ в_min, мВ |

-960 |

-1025 |

| Выходной, высокий, пороговый Uвыx_в_ пор, мВ |

-980 |

-1035 |

| Выходной, низкий, пороговый Uвыx_н_пор, мВ |

-1630 |

-1610 |

| Выходной, низкий, максимальный Uвых_н_maх, мВ |

-1650 |

-1620 |

| Выходной, низкий, минимальный Uвых_ н_min, мВ |

-1850 |

-1810 |

Рис. 1.7. Схема для измерения (а) параметров выходных импульсов (б)

Скорость переключения микросхем ЭСЛ удобно проверять при двуполярном напряжении питания (аналогично схеме включения операционного усилителя). При таком включении элемента ЭСЛ (см. рис. 1.7, а) источник входных импульсов можно заземлить. На рис, 1.7,6 обозначены уровни входного и выходных импульсов, по которым следует отсчитывать время задержки распространения при включении и отключении элемента, если входной импульс имеет заданную длительность фронта и среза. При замерах необходимо использовать кабели и нагрузки с сопротивлением 50 Ом. Несогласованные проводники не должны быть длиннее, чем 2 мм. К выходу схемы (рис. 1.7, а) требуется подключать вход согласованной линии передачи. При эксплуатации микросхем ЭСЛ необходимо учитывать дополнительно три временных параметра: ts-время «выдержки», th-время хранения и tr-время сброса.

Рис. 1.8. Особые временные параметры ЭСЛ: а- время выдержки ts; б - время хранения th; в - время сброса tr

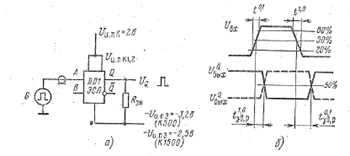

Для реализации ФУ нам потребуется счетчик, регистр. Ниже следует описание этих элементов ЭСЛ в серии К500.

Микросхемы К500ИЕ136 и К500ИЕ137 (рис. 1.9) - однотипные счетчики, отличающиеся выходными кодами: ИЕ136 считает в гексадецимальном коде, а ИЕ137 - в десятичном. Оба эти счетчика имеют универсальное назначение и могут при тактовых частотах свыше 100 МГц считать как на увеличение, так и на уменьшение выходных данных (реверс). Полная принципиальная схема микросхемы ИЕ136 показана на рис. 1.9, а, микросхемы ИЕ137 - на рис. 1.9,6. Их цоколевки одинаковы (см. рис. 1.9, в). Четыре режима работы этих счетчиков программируются по двум входам SI, S2 (см. табл. 1.2). Режим предварительной установки позволяет загрузить данные, присутствующие на входах DO-D3(см. также первую и восьмую строки табл. 1.3).

Таблица 1.2. Выбор режимов счетчиков К500ИЕ136 и ИЕ137

| Вход |

Режим |

| S1 S2 |

н н

н в

в н

в в

|

Предварительная установка

Счет на увеличение

Счет на уменьшение

Хранение; остановка счета (загрузка)

|

Счетчики меняют выходные состояния по положительному перепаду на тактовом входе С. В другие моменты (С=Н, см. пятую строку табл. 1.3) можно менять данные на входах D. После завершения счета на выходе окончания счета ТС устанавливается напряжение низкого уровня. Аналогично работает и счетчик К500ИЕ137 (см, табл. 1.4). Реверс счета получается при смене уровней напряжения на входах S1 и S2 (см. табл. 1.2) на противоположные.

Рис. 1.9. Счетчики серии К500: а - ИЕ136; б - ИЕ137; в - их цоколевка

Таблица 1.3. Состояния счетчика К500ИЕ136

| Вход |

Выход |

| S1 S2 |

D0 |

D1 |

D2 |

D3 |

С С |

Q0 |

Q1 |

Q2 |

Q3 |

|

| H Н |

Н |

Н |

В |

В |

Х |

В |

Н |

Н |

В |

В |

Н |

| H В |

X |

X |

X |

X |

Н |

В |

В |

Н |

В |

В |

В |

| H В |

X |

X |

X |

X |

Н |

В |

Н |

В |

В |

В |

В |

| H В |

X |

X |

X |

X |

Н |

В |

В |

В |

В |

В |

Н |

| Н В |

X |

X |

X |

X |

В |

Н |

В |

В |

В |

В |

В |

| Н В |

X |

X |

X |

X |

В |

В |

В |

В |

В |

В |

В |

| В В |

X |

X |

X |

X |

X |

В |

В |

В |

В |

В |

В |

| H H |

В |

В |

Н |

Н |

X |

В |

В |

В |

Н |

Н |

Н |

| В Н |

X |

X |

X |

X |

Н |

В |

Н |

В |

Н |

Н |

В |

| В Н |

X |

X |

X |

X |

Н |

В |

В |

Н |

Н |

Н |

В |

| В Н |

X |

X |

X |

X |

Н |

В |

Н |

Н |

Н |

Н |

Н |

| В Н |

X |

X |

X |

X |

Н |

В |

В |

В |

В |

В |

В |

Таблица 1.4. Состояния счетчика К500ИЕ137

| Вход |

Выход |

| S1 S2 |

D0 |

D1 |

D2 |

D3 |

С С |

Q0 |

Q1 |

Q2 |

Q3 |

|

| H Н |

В |

В |

В |

Н |

Х |

В |

В |

В |

В |

Н |

В |

| H В |

X |

X |

X |

X |

Н |

В |

Н |

Н |

Н |

В |

В |

| H В |

X |

X |

X |

X |

Н |

В |

В |

Н |

Н |

В |

Н |

| H В |

X |

X |

X |

X |

Н |

В |

Н |

Н |

Н |

Н |

В |

| Н В |

X |

X |

X |

X |

Н |

В |

В |

Н |

Н |

Н |

В |

| Н В |

X |

X |

X |

X |

В |

В |

В |

Н |

Н |

Н |

В |

| Н В |

X |

X |

X |

X |

В |

В |

В |

Н |

Н |

Н |

В |

| В В |

X |

X |

X |

X |

X |

В |

В |

Н |

Н |

Н |

В |

| Н Н |

В |

В |

Н |

Н |

Х |

В |

В |

В |

Н |

Н |

В |

| В Н |

X |

X |

X |

X |

Н |

В |

Н |

В |

Н |

Н |

В |

| В Н |

X |

X |

X |

X |

Н |

В |

В |

Н |

Н |

Н |

В |

| В Н |

X |

X |

X |

X |

Н |

В |

Н |

Н |

Н |

Н |

В |

При напряжениях высокого уровня на входах S1, S2 счет останавливается. Максимальная тактовая частота при счете, как на увеличение, так и на уменьшение составляет 125 МГц. Счетчики потребляют ток питания по 165 мА на корпус в каждом варианте. Наибольшее время задержки имеет цепь от входа С до выхода ТС. Наибольшее время «выдержки» ts=7,5 не требуется между сигналами на входах выбора S и тактовым С.

Микросхема К500ИР141 (рис. 1.10) -это регистр, который может работать в четырех режимах: остановка сдвига (хранение), сдвиг вправо, сдвиг влево, параллельный прием. Команда для выбора одного из режимов подается на входы выбора S1 и S2 согласно табл. 1.5. Сдвиг вправо и влево информации в триггерах получается после прихода положительного фронта тактового импульса tn+i на тактовый вход G (вывод 4). В табл. 1.5 данные Qn соответствуют предшествующему моменту tn. Регистр загружается параллельно по входам DO-D3, а по входам DL и DR последовательно для сдвига влево и вправо соответственно. Выходы QO-Q3 имеют нагрузочную способность 60 Ом. Если используется только один из выходов для последовательного вывода данных в нагрузку, остальные выходы следует оставить разомкнутыми.

Рис. 1.10. Регистр К500ИР141: а - схема; б – цоколевка

Таблица 1.5. Состояния регистра ИР141

| Вход выбора |

Режим работы |

Выход |

| SI S2 |

Q0(n+1) |

Q1(n+1) |

Q2(n+1) |

Q3(n+1) |

Н Н

Н В

В Н

В В

|

Параллельный прием

Сдвиг вправо

Сдвиг влево

Остановка сдвига

|

D0

DR

Q1(n)

Q0(n)

|

D1

Q0(n)

Q2(n)

Q1(n)

|

D2

Q1(n)

Q3(n)

Q2(n)

|

D3

Q2(n)

DL

Q3(n)

|

|