Синтез суммирующего асинхронного счетчика

Содержание

Введение

1. Характеристика проектируемого устройств

1.1 Назначение и особенности счетчиков

1.2 Анализ синтез JK - триггера

2. Анализ и синтез проектируемого устройства

2.1 Закон функционирования счётчика

2.2 Анализ работы счетчика

2.3 Синтез счётчика

3. Выбор и обоснование элементной базы счётчика

Заключение

Литература

Введение

Подсчет импульсов является одной из наиболее распространенных операций, выполняемых в устройствах дискретной обработки информации. Такая операция в цифровых устройствах выполняется с помощью счетчиков. Счетчиком называют цифровое устройство, предназначенное для подсчета числа импульсов. В процессе работы счетчик последовательно изменяет свое состояние в определенном порядке. Длина списка разрешенных состояний счетчика называется модулем счета Кс. Одно из возможных состояний счетчика принимается за начальное. Если счетчик начал счет от начального состояния, то каждый импульс, кратный модулю счета Кс, снова устанавливает счетчик в начальное состояние, а на выходе счетчика появляется сигнал переноса Р или займа..Z. Примером простейшего счетчика может служить счетный триггер, осуществляющий подсчет сигналов по модулю Ксч=2, так как он имеет два состояния 0 и 1, принимаемые им поочередно под действием входных сигналов. Таким образом, задача проектирования счетчиков сводится к разработке цифрового устройства, которое имело бы как минимум равное заданному модулю счета число устойчивых состояний и последовательно переходило из одного состояния в другое под действием поступающих импульсов. В общем случае устройство подобного вида может быть спроектировано с помощью формальных методов теории конечных автоматов. Однако следует отметить, что такие методы проектирования применяются в основном в том случае, когда требуется, чтобы счетчик работал в специальных кодах или выполнял переходы, закономерность которых сложно выполнить интуитивно.

Наряду с формальными известен целый ряд неформальных, а исключительно схемотехнических способов, позволяющих значительно упростить процедуру синтеза счетчика заданного вида по сравнению с классическими формальными является не только разработка той или иной схемы, удовлетворяющей предъявленным к ней требованиям, но и определение в некотором смысле оптимальной ее структуры, то разработчик должен владеть как схемотехническими, так и логическими методами синтеза. Умелое применение обоих методов и их сопоставление позволит выбрать оптимальный вариант синтезируемой..схемы. Задачей данной курсовой работы является синтез суммирующего асинхронного счетчика с типом триггеров JJJJ,Ксч=11 и в коде 6-3-2-1.

1. Характеристика проектируемого устройства

1.1 Назначение и особенности асинхронных счетчиков

Счетчики представляют собой более высокий, чем регистры, уровень сложности цифровых микросхем, имеющих внутреннюю память. Хотя в основе любого счетчика лежат те же самые триггеры, которые образуют и регистры, но в счетчиках триггеры соединены более сложными связями, в результате чего их функции - сложнее, и на их основе можно строить более сложные устройства, чем на регистрах. Точно так же, как и в случае регистров, внутренняя память счетчиков - оперативная, то есть ее содержимое сохраняется только до тех пор, пока включено питание схемы. С выключением питания память стирается, а при новом включении питания схемы содержимое памяти будет произвольным, случайным, зависящим только от конкретной микросхемы, то есть выходные сигналы счетчиков будут произвольными.

Как следует из самого названия, счетчики предназначены для счета входных импульсов. То есть с приходом каждого нового входного импульса двоичный код на выходе счетчика увеличивается (или уменьшается) на единицу. Срабатывать счетчик может по отрицательному фронту входного (тактового) сигнала (как на рисунке) или по положительному фронту. Режим счета обеспечивается использованием внутренних триггеров, работающих в счетном режиме. Выходы счетчика представляют собой как раз выходы этих триггеров. Каждый выход счетчика представляет собой разряд двоичного кода, причем разряд, переключающийся чаще других (по каждому входному импульсу), будет младшим, а разряд, переключающийся реже других, - старшим. Большинство счетчиков работают в обычном двоичном коде, то есть считают от 0 до (2N

–1), где N - число разрядов выходного кода счетчика.

Например, 4-разрядный счетчик в режиме прямого счета будет считать от 0 (код 0000) до 15 (код 1111), а 8-разрядный - от 0 (код 0000 0000) до 255 (код 1111 1111). После максимального значения кода счетчик по следующему входному импульсу переключается опять в 0, то есть работает по кругу. Если же счет - инверсный, то счетчик считает до нуля, а дальше переходит к максимальному коду 111...1.режим, имеющийся во всех счетчиках, он называется режимом прямого счета. Счетчик может также работать на уменьшение выходного кода по каждому входному импульсу; это режим обратного или инверсного счета, предусмотренный в счетчиках, называемых реверсивными. Инверсный счет бывает довольно удобен в схемах, где необходимо отсчитывать заданное количество входных импульсов. Счетчик обычно реализуется на триггерах. Имеются также двоично-десятичные счетчики, предельный код на выходе которых не превышает максимального двоично-десятичного числа, возможного при данном количестве разрядов. Например, 4-разрядный двоично-десятичный счетчик в режиме прямого счета будет считать от 0 (код 0000) до 9 (код 1001), а затем снова от 0 до 9. А 8-разрядный двоично-десятичный счетчик будет считать от 0 (код 0000 0000) до 99 (код 1001 1001). При инверсном счете двоично-десятичные счетчики считают до нуля, а со следующим входным импульсом переходят к максимально возможному двоично-десятичному числу (то есть 9 - для 4-разрядного счетчика, 99 - для 8-разрядного счетчика). Двоично-десятичные счетчики удобны, например, при организации десятичной индикации их выходного кода. Применяются они гораздо реже обычных двоичных счетчиков. По быстродействию все счетчики делятся на три большие группы:

· Асинхронные счетчики (или последовательные).

· Синхронные счетчики с асинхронным переносом

· Синхронные счетчики (или параллельные).

Счетчик может также работать на уменьшение выходного кода по каждому входному импульсу; это режим обратного или инверсного счета, предусмотренный в счетчиках, называемых реверсивными. Инверсный счет бывает довольно удобен в схемах, где необходимо отсчитывать заданное количество входных импульсов.

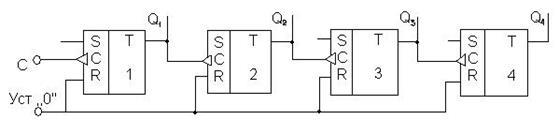

Простейшая схема с последовательным переносом, построенная на Т-триггерах, представлена на этом рисунке 1:

Рис. 1. Схема двоичного счетчика

Триггеры в этой схеме переключаются из одного положения в другое при переходе уровня сигнала на счетном воде с высокого на низкий. Выработка переноса определяется условием Триггеры в этой схеме переключаются из одного положения в другое при переходе уровня сигнала на счетном воде с высокого на низкий. Выработка переноса определяется условием

Вычитающий счетчик предназначен для выполнения счета в обратном направлении, т.е. в режиме вычитания. Каждый счетный импульс, поступивший на вход такого счетчика, уменьшает его показания на единицу.

Реверсивным называются такие счетчики, которые предназначены для выполнения счета как в прямом, так и в обратном направлении, т.е. могут работать в режиме сложения и в режиме вычитания.

По способу переключения разрядов счетчики классифицируются:

Техническая характеристика счетчика

Основными характеристиками счетчиков являются:

- модуль счета или коэффициент пересчета счетчика ( ); );

- быстродействие счетчика;

- разрешающая способность;

- информационная емкость

Модуль счета (или коэффициент пересчета) характеризует число устойчивых состояний счетчика, т.е. предельное число импульсов, которое может быть сосчитано счетчиком. Например, при  счетчик будет иметь 8 устойчивых состояний и каждый восьмой импульс, поступающий на его вход, будет возвращать счетчик в первоначальное состояние. счетчик будет иметь 8 устойчивых состояний и каждый восьмой импульс, поступающий на его вход, будет возвращать счетчик в первоначальное состояние.

Быстродействие счетчика характеризуется параметрами:

- частотой поступления счетных импульсов; - частотой поступления счетных импульсов;

- временем установки счетчика. - временем установки счетчика.

Параметр  характеризует максимальную частоту поступления счетных импульсов на вход счетчика. характеризует максимальную частоту поступления счетных импульсов на вход счетчика.

Для счетчиков, срабатывающих по уровню тактового импульса, время установки кода характеризует максимальный временной интервал между моментами поступления счетного импульса и моментом установления кода счетчика. Для счетчиков, работающих в режиме с внутренней задержкой,  определяется максимальным временным интервалом между моментом окончания счетного импульса и моментам установления кода счетчика. Предполагается, что считывание кода осуществляется параллельно со всех разрядов счетчика. определяется максимальным временным интервалом между моментом окончания счетного импульса и моментам установления кода счетчика. Предполагается, что считывание кода осуществляется параллельно со всех разрядов счетчика.

В счетчиках, построенных на счетных триггерах с внутренней задержкой переключение разрядов происходит после окончания счетного импульса.

Разрешающая способность – это минимальное время между двумя сигналами, которое надежно фиксируются счетчиком. Максимальное быстродействие счетчика – величина, обратная разрешающей способности и равная числу сигналов, которое может быть подсчитано счетчиком в единицу времени.

Информационная емкость – максимальное число сигналов, которое может быть подсчитано счетчиком. Количественно емкость счетчика равна коэффициенту пересчета Ксч.

Асинхронные счетчики строятся из простой цепочки JK-триггеров, каждый из которых работает в счетном режиме. Выходной сигнал каждого триггера служит входным сигналом для следующего триггера. Поэтому все разряды (выходы) асинхронного счетчика переключаются последовательно (отсюда название - последовательные счетчики), один за другим, начиная с младшего и кончая старшим. Каждый следующий разряд переключается с задержкой относительно предыдущего, то есть, вообще говоря, асинхронно, не одновременно с входным сигналом и с другими разрядами.

Чем больше разрядов имеет счетчик, тем большее время ему требуется на полное переключение всех разрядов. Задержка переключения каждого разряда примерно равна задержке триггера, а полная задержка установления кода на выходе счетчика равна задержке одного разряда, умноженной на число разрядов счетчика. Легко заметить, что при периоде входного сигнала, меньшем полной задержки установления кода счетчика, правильный код на выходе счетчика просто не успеет установиться, поэтому такая ситуация не имеет смысла. Это накладывает жесткие ограничения на период (частоту) входного сигнала, причем увеличение, к примеру, вдвое количества разрядов счетчика автоматически уменьшает вдвое предельно допустимую частоту входного сигнала. Возьмём на примере асинхронного суммирующего счётчика и рассмотрим его работу.

Суммирующий счетчик может быть реализован на асинхронных триггерах со счетным Т-входом, как это изображено на рис. 2, а. Триггер Т1 переключается по каждому сигналу Т; сигнал Q1

на его выходе является входным для триггера Т2; сигнал Q2

на выходе Т2 является входным для ТЗ. Временная диаграмма на рис. 2, б поясняет работу счетчика. Если начальное состояние счетчика равно 000, то после первого сигнала Т его состояние будет 001 (Т1 является младшим разрядом счетчика, ТЗ — старшим), после второго — 010 и т. д.

После восьмого сигнала Т состояние счетчика будет снова 000. Максимальное число, которое может быть представлено п-разрядным счетчиком, равно N2

= 11 ... 11 или в десятичной системе счисления N10

= 2n

— 1. Это значение называют емкостью счетчика.

Рис.2 Суммирующий счетчик на асинхронных триггерах со счетным Т-входом

Рассмотренный счетчик называют асинхронным, так как после воздействия сигнала Т на его входе триггеры переключаются в новое состояние последовательно. Асинхронный счетчик часто называют также счетчиком с последовательным переносом.Если задержка переключения вспомогательных триггеров относительно момента окончания входного сигнала равна тТ2

, то задержка переключения л-го триггера счетчика относительно момента окончания сигнала Т при переключении счетчика из состояния 11... 11 в состояние 00...00, называемая временем установления показания, составит величину tУ

CT

=

Следовательно, время выполнения микрооперации счета в асинхронном счетчике, имеющем п разрядов, будет равно tC

4

= tc

+ п тТ2

, где tc

— Длительность сигнала Т на счетном входе счетчика.

Если триггеры в схеме счетчика, показанной на рис.2, отсоединить так, что сигнал  будет входным для Т2, а сигнал будет входным для Т2, а сигнал  — входным для ТЗ, получим вычитающий счетчик, содержимое которого после каждого сигнала Т будет уменьшаться на единицу. — входным для ТЗ, получим вычитающий счетчик, содержимое которого после каждого сигнала Т будет уменьшаться на единицу.

Недостатком асинхронных счетчиков является увеличение значения tуст

с ростом числа разрядов счетчика п.

1.2 Анализ и синтез JK - триггера

Триггер - это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется.

Как правило, триггер имеет два выхода: прямой и инверсный. Число входов зависит от структуры и функций, выполняемых триггером. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может записываться непрерывно и определяется информационными сигналами, действующими на входах в данный момент времени. Если информация заносится в триггер только в момент действия так называемого синхронизирующего сигнала, то такой триггер называют синхронизируемым или тактируемым. Помимо информационных входов тактируемые триггеры имеют тактовый вход, вход синхронизации. На примере рассмотрим анализ и синтез JK триггера.

JK–триггер является одним из универсальных триггеров и имеет два информационных входа J и K. Для установки триггера в “1” необходимо подать синхроимпульс при наличии на входе J сигнала “1”, а на входе К – “0”. Поступление синхроимпульса при J = “0”, К = “1” приводит к переключению триггера в нулевое состояние. Схема JK–триггера и временная диаграмма представлены на рисунке 3.

Рисунок 3. JK- триггер

При одновременной подаче сигнала “1” на входы J и K по каждому синхроимпульсу JK–триггер изменяет свое состояние на противоположное, т.е. работает в счетном режиме.

JК-триггеры подразделяются на универсальные и комбинированные. Универсальный JК -триггер имеет два информационных входа J и К. По входу J триггер устанавливается в состояние Q = 1,  = 0, а по входу К – в состояние Q = 0, = 0, а по входу К – в состояние Q = 0,  = 1. = 1.

JК-триггер отличается от RS-триггера прежде всего тем, что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

Комбинированный JК-триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0).

Простейший JК-триггер можно получить из синхронного RS-триггера, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний. Если входы J, К и С объединить, то получим Т-триггер, который переключается каждым входным импульсом.

При входных сигналах J = К = 0 состояние триггера не изменяется, так как напряжение низкого уровня на одном входе элемента И-НЕ отменяет прохождение сигналов от других его входов и удерживает выходной сигнал на высоком уровне. Если на входы J и К подать взаимно противоположные уровни, то при подаче перепада напряжения на вход С выходы JК-триггера устанавливаются такие же состояния. При подаче на входы J и К одновременно напряжении высокого уровня триггер переключается в состояние, противоположное предыдущему, если на вход синхронизации С подать перепад напряжения.

2. Анализ и синтез счетчика

2.1 Анализ счетчика

Один из методов проектирования счетчиков с заданным коэффициентом счета заключается в построении таблицы переходов, в первых столбцах которых будут отражены текущие состояния триггеров счетчика, а в последующих - следующие за ними состояния. Анализ таблицы позволяет установить те переходы, которые должны быть “сделаны” триггерами, входящими в состав счетчика. Затем с помощью управляющей таблицы соответствующего триггера находятся значения логических функций на управляющих входах триггеров, позволяющие осуществить эти переходы.

Синтезируем суммирующий асинхронный счетчик с Ксч

=11, работающий в коде 6-3-2-1 на JJJJ триггерах.

Число разрядов, необходимое для возможности подсчета Ксч

импульса определяется по формуле:

M=[log2(Kсч+1)]

Следовательно:

M=log2(12+1)=4

Определим число избыточных комбинаций:

42=16;

16-12=2.

Таблица 1

Таблица содержит номер комбинации, которое соответствует числу в десятичной системе счисления(N), используемый код и соответствующие ему выходы, а также разрешающие сигналы для каждого триггера (С4,С3,С2,С1).Столбец Q1 соответствует двоичному разряду единиц или самой младшей значащей цифре (младший разряд). Столбец Q4 соответствует двоичному разряду семерок или старшей значащей цифре (старший разряд).

Столбцы с разрешающими сигналами (С1,С2,С3,С4) заполняются по принципу: 1 ставится в том случае, если в соответствующем разряде Q происходит переход из1 в 0 либо из 0 в 1, если же разряд сохраняется, то разрешающий сигнал отсутствует.

Составляем прикладные карты Карно, которые отображают переход функции из одного такта в другой:

Для функции Q1: при переходе данной функции из нулевого такта в первый она меняет свое значение с нуля на единицу. По этому в клеточке Q2Q3Q4 мы пишем 11. Если функция не меняет своего значения (например, при переходе функции из второго такта в третий значение сохраняется: 00), то мы пишем в соответствующей клеточке «Х».

Аналогично заполняются прикладные карты Карно для функций Q1

n

+1

, Q2n+1,Q3n+1,Q4n+1.

2.3 Синтез счетчика

Заполняем диаграммы Вейча для уравнений кодов с использованием прикладных диаграмм Вейча и таблиц переходов для JK и D-триггеров.

Таблица переходов для JK- и D-триггеров:

Таблица 2

Используем данную таблицу и прикладные карты Карно Q1

n

+1

, Q2

n

+1

, Q3

n

+1

,Q4

n

+1

для нахождения J1

и K1

, J2

и K2

, J3

и K3

, J4

и K4

:

| Q1

|

Q1

|

Q1

|

Q1

|

| Q2

|

х |

х |

0 |

1 |

Q2

|

x |

х |

x |

x |

Q2

|

1 |

х |

x |

x |

Q2

|

х |

х |

1 |

х |

| х |

х |

х |

0 |

Q4

|

х |

х |

х |

x |

Q4

|

х |

х |

х |

1 |

Q4

|

х |

х |

х |

х |

Q4

|

| x |

x |

1 |

1 |

1 |

0 |

0 |

0 |

х |

x |

х |

х |

х |

x |

х |

х |

| x |

x |

x |

1 |

1 |

1 |

х |

0 |

х |

х |

х |

х |

х |

х |

х |

х |

| Q3

|

Q3

|

Q3

|

Q3

|

Рис. 8 Карта Рис. 9 Карта Рис. 10 Карта Рис. 11 Карта

Карно для J1

Карно J2 Карно для J3 Карно для J4

| Q1

|

Q1

|

Q1

|

Q1

|

| Q2

|

х |

х |

0 |

1 |

Q2

|

x |

х |

x |

x |

Q2

|

1 |

х |

x |

x |

Q2

|

х |

х |

1 |

х |

| х |

х |

х |

0 |

Q4

|

х |

х |

х |

x |

Q4

|

х |

х |

х |

1 |

Q4

|

х |

х |

х |

х |

Q4

|

| x |

x |

1 |

1 |

1 |

0 |

0 |

0 |

х |

x |

х |

х |

х |

x |

х |

х |

| x |

x |

x |

1 |

1 |

1 |

х |

0 |

х |

х |

х |

х |

х |

х |

х |

х |

| Q3

|

Q3

|

Q3

|

Q3

|

Рис. 8 Карта Рис. 9 Карта Рис. 10 Карта Рис. 11 Карта

Карно для J1

Карно J2 Карно для J3 Карно для J4

J1

= Q2

+(Q1

*Q3

*Q4

)

K1

= Q2

J2

= Q1

*Q3

+Q1

*Q2

*Q4

K2

= Q1

+Q3

+Q4

J3

= 1

K3

= 1

J4

= 1

K4

= 1

По таблице переходов (таблица 1) определяем чему будут равны значения динамических входов С:

C1=Tc;

C2=Tc;

C3= Q2

n

;

C4=Q3

n

.

Используя эти данные и результаты минимизации построим электрическую функциональную схему (ГЧ, лист 1) и временную диаграмму (ГЧ, лист 2).

По таблице переходов (таблица 1) определяем чему будут равны значения динамических входов

С:

C1= ; ;

C2=Q1;

C3= TC1;

C4= Q3.

Используя эти данные и результаты минимизации построим электрическую функциональную схему (ГЧ, лист 1) и временную диаграмму (ГЧ, лист 2).

C4= Q3.

Рис. 12 Условное обозначение микросхемы типа ТВ1

Микросхема К561ТВ1 содержит по два независимых JK-триггера. Структурная схема одного JK-триггера приведена на рисунке 13

Триггер имеет асинхронные R и Sвходы. Поступление высокого уровня на один из этих входов на время, превышающее 120 нс, переключает триггер соответственно в «0» или «1». Если высокий уровень присутствует на обоих входах Rи S, то на выходах Qи  также будут высокие уровни. также будут высокие уровни.

Входы J и К являются синхронными с входом С. Присутствие высокого уровня на входе J или К приводит к переключению триггера соответственно в «1> и «0> по переднему фронту импульса синхронизации на входе С, длительность которого должна быть не менее 170 нc, а длительность которого должно быть не менее 170 нc,а длительность фронта и среза (нарастания и спада) не должна быть более 5 мкс.

При одновременном присутствии высоких уровней на входах J и К триггер будет изменять свое состояние на противоположное по каждому импульсу синхронизации, т. е. осуществлять синхронный счетный режим.

При соединении входов J, К и С вместе и подачи на них входных импульсов с достаточно крутыми фронтами будет осуществляться асинхронный счетный режим, т. е. переключение триггера в противоположное состояние по фронту каждого входного импульса. Максимальная частота в таком режиме составляет 3 мГц, при Um

= 10 В.

Микросхема КР1561ЛИ2 содержит четыре логических элемента 2И, реализуемые, инвертированием выходного сигнала элемента 2И-НЕ. Условное обозначение ИС и её цоколевка изображены на рисунке 14.

Рис. 14 Условное обозначение микросхемы типа ЛИ2

Микросхема типа ЛЕ5 выполняет логическуюфункцию mИЛИ-НЕ, где m— количество входов. Реализация её обеспечивается последовательным соединением mМДП-транзисторов с каналом р-типа и параллельным соединением mМДП-транзисторов с каналом n-типа. На рисунке 15 приведена принципиальная электрическая схема и таблица состояний логического элемента 2ИЛИ-НЕ, являющегося одним из элементов ИС ЛЕ5.

Рис.15 Принцип реализации КМДП ИС типа ЛЕ:

а -двухвходовый элемент ИЛИ ; б – таблица состояний схемы

Этот тип элементов также имеет более высокий уровень U0вых и более низкий уровень U1вых, по сравнению с простейшим КМДП-инвертором. Чтобы величина U1вых не была ниже предельно допустимого уровня, ширина каналов МДП-транзисторов с каналом р-типа (по схеме рис. 11 VT1 и VT2) больше в mраз, чем у МДП-транзисторов с каналом n-типа.

Каждая из микросхем типа ЛЕ содержит от 2 до 4 логических элементов mИЛИ-НЕ. Количество элементов в корпусе определяется количеством выводов. Цоколевки и условные обозначения ИС типа ЛЕ5 приведены на рисунке 16.

Рис. 16 Условное обозначение микросхемы Типа ЛЕ5

Заключение

В данной курсовой работе я синтезировал суммирующий асинхронный счетчик с КСЧ

=11 в коде 6-3-2-1и с типом триггеров JJJJ . В ходе решения курсовой работы я изучил:

-характеристику данного счетчика;

-особенности и назначение;

-анализ и синтез JK - триггера;

-анализ и синтез проектируемого счётчика;

В ходе работы исследовал, что подсчет импульсов является одной из наиболее распространенных операций, выполняемых в устройствах дискретной обработки информации. Такая операция выполняется с помощью счетчиков. По целевому назначению счетчики подразделяются на простые и реверсивные. Простые счетчики, в свою очередь, подразделяются на суммирующие и вычитающие.

Литература

1. Богданович М.И., Грель и.Н. Цифровые интегральные микросхемы.

2. Букреев И.Н. Микроэлектронные схемы цифровых устройств. 3. Курс лекций по дисциплине “Основы проектирования ”.4. Орлов И.А., Корнюшенко В.Ф. Основы вычислительной техники и организация вычислительных работ. 5. Путков В.Н., И.И. Обросов, С.В. Бекетов. Электронные вычислительные устройства, 1981.

6. Токхейм Р. Основы цифровой электроники

7. Устаченко С.Т., Терехова М.В. Выполнение электрических схем на ЕСКД.

|