| БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ

Кафедра метрологии и стандартизации

РЕФЕРАТ

На тему:

"Векторные анализаторы цепей. Контроль и диагностика компонентов цифровых сетей и систем телекоммуникаций"

МИНСК, 2008

Векторные анализаторы цепей.

Гетеродинные векторные анализаторы цепей

Гетеродинные векторные анализаторы цепей строятся на базе скалярных анализаторов цепей. СВЧ измерительный тракт остается практически таким же, а так как при амплитудном детектировании информация о фазе теряется, то вместо амплитудных детекторов используется СВЧ смесители или стробоскопические преобразователи частоты.

У гетеродинных ВАЦ используется 2 СВЧ генератора с различными частотами.

Обобщенная структурная схема ВАЦ для режима измерения S21 (S12) представлена на рисунке 1.

Важнейшими узлами таких ВАЦ являются смесители. Они должны иметь хорошую развязку каналами.

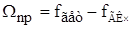

На выходах смесителей выделяется сигнал промежуточной частоты:

Постоянство  обеспечивает схема фазовой автоподстройки частоты (ФАПЧ), которая работает по сигналу опорного сигнала (ОК). В процессе работы гетеродин перестраивается синхронно с ГКЧ. обеспечивает схема фазовой автоподстройки частоты (ФАПЧ), которая работает по сигналу опорного сигнала (ОК). В процессе работы гетеродин перестраивается синхронно с ГКЧ.

Выходные сигналы смесителей опорного и измерительного каналов (ИК) поступают на векторный измеритель отношений, где производится измерение отношений их амплитуд, а с помощью фазового детектора – разность фаз сигналов. После усиления и детектирования сигналы подаются на ЭЛТ, где производятся наблюдения исследуемых характеристик. Причем индикация может осуществляться двумя способами:

1) в полярных координатах (для S11, S22).

2) в декартовых координатах (в виде частотных характеристик всех S-параметров).

К достоинствам гетеродинных ВАЦ можно отнести большой динамический диапазон (80-90 дБ), а к недостаткам, сложность СВЧ оборудования и высокую стоимость.

Источники погрешностей практически те же, что и в скалярных, но в векторных АЦ предъявляются очень жесткие требования к точности установки и нестабильности частоты ГКЧ.

Гомодинные векторные анализаторы цепей

В этих ВАЦ используется только один генератор, а для получения информации о фазе измеряемого параметра используется дискретный фазовращатель. В гомодинных ВАЦ используется относительно простое СВЧ оборудование, но более сложные алгоритмы обработки измерительной информации.

Упрощенная схема гомодинного ВАЦ для режима измерения S21, S12 представлена на рисунке 2.

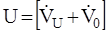

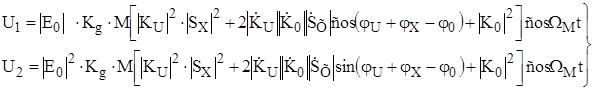

На выходе СВЧ-сумматора ( ) имеем сигнал векторной суммы: ) имеем сигнал векторной суммы:  , ,

где  и и  сигналы измерительного (ИК) и опорного (ОК) каналов. сигналы измерительного (ИК) и опорного (ОК) каналов.

Эти сигналы описываются следующими выражениями:

, ,

, ,

где Е0 – амплитуда поля в точке разветвления ОК и ИК,

– модули и аргументы коэффициентов передачи измерительного и опорного каналов и объекта измерения соответственно. – модули и аргументы коэффициентов передачи измерительного и опорного каналов и объекта измерения соответственно.

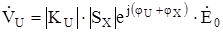

Для двух положений дискретного фазовращателя (ДВФ) можно записать:

,(1) ,(1)

где  - коэффициент и частота амплитудной модуляции ГКЧ, - коэффициент и частота амплитудной модуляции ГКЧ,

Kg - коэффициент передачи сумматора и детектора.

Из уравнения (1) можно найти значения Sx и jx, определив при калибровке анализатора другие, входящие в (1) величины.

К достоинствам гомодинных ВАЦ можно отнести значительно более простой измерительный тракт СВЧ, а к недостаткам более сложные алгоритмы измерения и калибровки и меньший динамический диапазон измерений (≈50 дБ) по сравнению с гетеродинными ВАЦ.

Контроль и диагностика компонентов цифровых сетей и систем телекоммуникаций

Общие сведения и классификация методов измерения

Испытания цифровых схем, микропроцессоров и микропроцессорных систем называют тестированием. Его проводят с целью проверки качества функционирования цифрового устройства или системы, диагностики и отыскания неисправностей. Сложность, а иногда и невозможность использования для этих целей традиционных методов измерения и приборов обусловлено следующими причинами:

– многоканальность (иногда надо просмотреть одновременно до 64 логических процессов);

– сложность наблюдения однократных и непериодических процессов;

– сложность, а иногда и невозможность синхронизации осциллографа;

– очень большая трудоемкость и высокая квалификация операторов.

Эти причины обусловили разработку новых эффективных методов тестирования. Основными из них являются:

– программная автодиагностика;

– статическое тестирование;

– логический анализ;

– сигнатурный анализ.

Программная автодиагностика предполагает тестирование программируемых устройств на основе использования внутренних диагностических программ. Они бывают двух видов:

– самозапускаемые;

– вызываемые по требованию оператора.

Использование автодиагностики предусматривают при проектировании системы и указания по ее осуществлению отражают в соответствующей инструкции.

Метод статического тестирования микропроцессорной системы основан на том, что выполняемые ею операции можно рассматривать как совокупность последовательно изменяемых электрических состояний. Поэтому, если пользователи не интересует динамика процесса, то систему можно тестировать искусственно, устанавливая различные состояния. Для этого в систему включают специальные устройства, содержащие набор переключателей, с помощью которых можно создавать все возможные состояния.

Логический анализ.

Принцип действия и классификация логических анализаторов

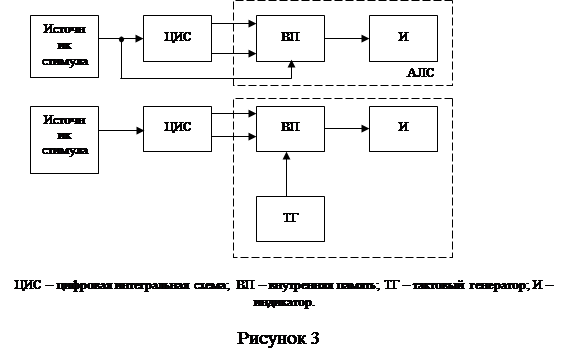

Принцип действия логических анализаторов заключается в том, что изменения логических состояний в исследуемых точках, переход из одного логического состояния в другое под воздействием внешних стимулов записываются во внутреннюю память анализатора, а затем воспроизводятся на экране в виде удобном для восприятия оператором. Наличие в анализаторе внутренней памяти позволяет просматривать не только периодические, но и однократные логические процессы. В зависимости от наличия внутреннего генератора и вида индикации логические анализаторы делятся на: анализаторы логических состояний (АЛС) и анализаторы временных диаграмм (АВД).

Структурные схемы использования АЛС и АВД приведены на рисунке 3.

АЛС используется для записи во ВП сигналов внешних по отношению к прибору. Для записи этих сигналов используются стимулирующие сигналы, изменяющие логические состояния исследуемых схем.

В АВД для записи сигналов используется внутренний ТГ.

Таким образом, при помощи логических анализаторов данные о логических состояниях исследуемых схем заносятся во ВП, преобразуются к виду удобному для поступления на индикатор и индицируются для АЛС в виде таблицы истинности, для АВД в виде квазивременной диаграммы.

В АЛС данные в память заносятся синхронно с изменением логического состояния исследуемого устройства, поэтому АЛС называют синхронными анализаторами.

В синхронном режиме логический анализатор работает от генератора тактовых импульсов исследуемой схемы.

В АВД данные в память заносятся асинхронно, поэтому их называют асинхронными анализаторами.

В асинхронном режиме для записи во внутреннюю память используются сигналы внутреннего тактового ТГ. Чтобы избежать потерь записи информации частота этого генератора должна быть в 4-10 раз больше частоты исследуемой схемы. Кроме того ВП в АВД всегда много больше, чем в АЛС. Например, наибольшая глубина памяти в современных АЛС – 64 бита/канал, а в АВД может быть 2048 б/канал и больше.

Обобщенная структурная схема логического анализатора

Обобщенная структурная схема логического анализатора приведена на рисунке 4.

Эта схема верна и для АЛС и для АВД. Тактовые импульсы могут быть и внешними и внутренними.

Назначение блоков

К0,…, Кn сортируют поступающую информацию на логический "0" или "1".

В П0,…, Пn записывается информация при помощи внешнего для АЛС или внутреннего для АВД тактового импульса.

КК сравнивает поступающую информацию с информацией, вводимой с передней панели анализатора. При приходе запускающего слова он вырабатывает сигнал на устройство запуска.

УЗ разрешает запись в память приходящей информации.

СЗЗ задерживает разрешение записи в память на заданное число запускающих слов.

СЦЗ задерживает разрешение записи на заданное число тактовых импульсов.

СПИ преобразует информацию записанную в памяти к виду удобному для восприятия.

И индицирует информацию в виде таблицы истинности или квазивременной диаграммы. И индицирует информацию в виде таблицы истинности или квазивременной диаграммы. И индицирует информацию в виде таблицы истинности или квазивременной диаграммы. И индицирует информацию в виде таблицы истинности или квазивременной диаграммы.

| К0

,…,Кn

– компараторы; П0

,…,Пn

– память; СПИ – схема преобразования

информации; КК – компаратор кодов; УЗ – устройство запуска; СЗЗ – счетчик

задержки запуска; СЦЗ – счетчик цифровой задержки.

|

|

Для нормальной работы анализатора надо с передней его панели ввести следующие данные:

- вид индикации;

- режим работы;

- код запускаемого слова;

- длительность задержки записи;

- длительность цифровой задержки;

- уровень компарирования (с учетом уровней логических сигналов исследуемой схемы);

- частоту внутреннего ТГ (для АВД) и другие.

Современные логические анализаторы выполняются с числом каналов от 2 до 128, как правило с дискретом 2,4,8, и так далее.

Большинство АЛС имеют быстродействие 10-50 МГц. Частота современных АВД – от 50 до 500 МГц. Чем выше рабочая частота анализатора, тем более узкие импульсы он способен захватывать. Например, анализатор с быстродействием 50 МГц различает “паразитные” импульсы длительностью 5-10 нс, а с быстродействием 100 МГц - 3÷5 нс.

АВД чаще используется на начальной стадии проектирования при отладке аппаратных средств. Благодаря большой глубине памяти и специальной схеме детектирования коротких импульсов при помощи его можно отыскать короткие "паразитные" импульсы. На конечной стадии проектирования при отладке математического обеспечения систем чаще используются АЛС, на экране которых мы можем отображать фрагменты программы в двоичном коде. Некоторые АЛС имеют дополнительные блоки преобразования информации, что позволяет получать на экране таблицу команд непосредственно на языке программирования высокого уровня.

Индикация в логических анализаторах

В портативных логических анализаторах используется однострочная индикация на светодиодах или светодиодных семисегментных индикаторах. На них высвечивается одно параллельное слово. Дальнейший просмотр содержимого памяти производится построчно.

В многоканальных логических анализаторах используется дисплей, выполненный на основе ЭЛТ. В них индикация может осуществляться в виде:

1) таблицы чисел (таблица истинности);

2) временных диаграмм;

3) карты состояний;

4) графов.

Индикация в виде таблицы истинности осуществляется в различных форматах или системах счисления (двоичном, восьмеричном или шестнадцатеричном). Картину на дисплее при индикации в двоичном формате иллюстрирует рисунок 5.

По горизонтали расположены слова, а вертикальная ось называется “осью событий”. Таким образом, табличный дисплей воспроизводит информацию в координатах “слово – событие”. Пример события – очередной тактовый импульс, изменяющий состояние схемы.

Для удобства чтения слова, состоящее из 12 бит, разделяют на части (слоги), содержащие по 4 бита для шестнадцатеричного кода и по 3 бита для восьмеричного кода.

Экран дисплея, на котором отображается логические временные диаграммы, подобен экрану многоканального осциллографа.

Обычно можно наблюдать восемь временных диаграмм (в координатах “напряжение – время”).

Пример отображения информации во временной области представлен на рисунке 6.

При представлении данных в виде карты состояний отдельное 16-разрядное слово преобразуется в точку или штрих, расположение которых на экране говорит о его содержимом. Такой вид индикации дает общее качественное представление обо всей информации, проходящей через анализатор.

Структурная схема преобразования информации в карту состояния представлена на рисунке 7.

Вся информация разбивается на две группы по 8 каналов. Информация с каждой группы поступает на цифроаналоговые преобразователи (ЦАП), выходы которых связаны с горизонтально и вертикально отклоняющими пластинами ЭЛТ.

Таким образом, каждому 16-разрядному слову соответствует единственная точка или штрих с вполне определенными координатами.

Такой вид индикации используется для общей оценки программы, проходящей по шине. При этом на экране можно увидеть петли программы, по яркости найти наиболее часто встречающие слова, по мерцанию отдельных точек найти перемежающиеся сбои.

При появлении подозрительных мест в программе можно сделать переход на индикацию в виде таблицы истинности для более детального анализа программы.

Кроме логических анализаторов общего применения выпускают анализаторы специализированные для работы с отдельными типами микропроцессоров. В них индикация осуществляется в виде команд на языке программирования для данного типа микропроцессора. В качестве индикатора используется алфавитно-цифровой дисплей. Другим типом специализированного логического анализатора является анализатор логических состояний КОП 814.

ЛИТЕРАТУРА

1. Метрология и электроизмерения в телекоммуникационных системах: Учебник для вузов /А.С. Сигов, Ю.Д. Белик. и др. / Под ред. В.И. Нефедова. – 2-е изд., перераб. и доп. – М.: Высш. шк., 2005.

2. Бакланов И.Г. Технологии измерений в современных телекоммуникациях. – М.: ЭКО-ТРЕНДЗ, 2007.

3. Метрология, стандартизация и измерения в технике связи: Учеб. пособие для вузов / Под ред. Б.П. Хромого. – М.: Радио и связь, 2006.

|