Содержание

Введение

1. Структурная схема системы

1.1 Анализ технического задания

1.2 Структурная схема устройства

1.3 Описание микроконтроллера i8086

2. Разработка и описание схемы

2.1 Процессорный блок

2.2 Расчет ОЗУ

2.3 Описание адаптера параллельного интерфейса

2.4 Программирование адаптера параллельного интерфейса

Вывод

Введение

В настоящее время происходит очень быстрое развитие компьютерных технологий. Большинство цифровых систем строится на микропроцессорах или на микроконтроллерах. Управление различными технологическими процессами происходит при помощи микропроцессорных систем или при помощи технологических операций. Данные системы практически универсальны, так как они имеют очень высокое быстродействие и достаточную разрядность для обработки информации на производстве.

Микропроцессор представляет собой функционально законченное устройство, состоящее из одной или нескольких программно-управляемых БИС и служит для выполнения операций по обработке информации и управления вычислительным процессом. Центральное место в структуре микропроцессорного устройства занимает микропроцессор, который выполняет арифметические и логические операции над данными, программное управление процессором обработки информации, а также организует взаимодействие всех устройств, входящих в систему.

Для реализации устройств обработки информации (УОИ) используют аппаратные, программные, программные и аппаратно-программные средства. При аппаратных получают устройство обработки информации с «жесткой» логикой, что обеспечивает наибольшее быстродействие, но требует большие аппаратные затраты. При программных УОИ реализуется в виде программы для типовой универсальной микро-ЭВМ, предназначенной для встраивания непосредственно в разрабатываемые блоки. При аппаратно-программных предполагается разработка как программных, так и аппаратных средств на базе микропроцессоров (МП).

В данной расчетно-графической работе будет рассмотрен микроконтроллер i8086. Для этого необходимо знать архитектуру БИС и микропроцессорного комплекта, представлять взаимодействие БИС в системе и овладеть программированием, прежде всего на языке ассемблера.

1. Структурная схема системы

1.1 Анализ технического задания

Необходимо разработать микропроцессорную систему обработки данных на базе микроконтроллера i8086. Система кроме процессорного блока включает блок памяти, информационная емкость ОЗУ которого составляет 4К´16 бит.

| Тип микроконтроллера |

Количество

ячеек внешнего

ОЗУ, Кбайт

|

Количество входов параллельного интерфейса |

Количество выходов параллельного интерфейса |

Реж.

0

|

Реж.

1

|

Реж.

2

|

Реж.

0

|

Реж.

1

|

Реж.

2

|

| i8086 |

0, 512 |

8 |

16 |

1.2 Структурная схема устройства

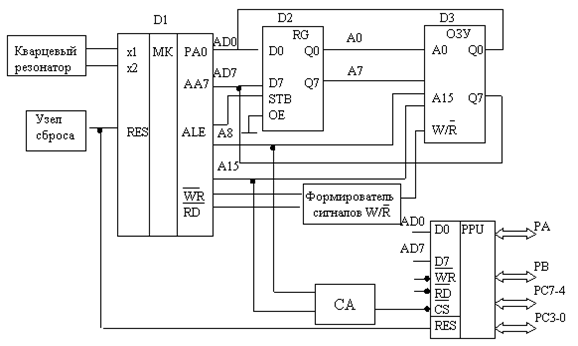

Система состоит из микроконтроллера i8086, порты которого используются для вывода адреса ОЗУ, подключен адаптер параллельного интерфейса i8255. Взаимодействие микроконтроллера с внешней памятью и периферийными устройствами осуществляется по шине адреса. Данные передаются и принимаются микроконтроллером по шине данных. Управляющие сигналы передаются по шине управления.

ОЗУ подключены своими адресными входами к шине адреса и передают и принимают данные по шине данных. Адрес формируется на контактах портов РА – 8 младших разрядов и РС – старшие разряды. Обмен данными с ОЗУ микроконтроллер осуществляет через порт РА. Поэтому младшие разряды адреса на время обмена сохраняются на время обмена в регистре-защелке.

Структурная схема устройства приведена ниже на рис.1.

Рис.1 Структурная схема системы

1.3 Описание микроконтроллера i8086

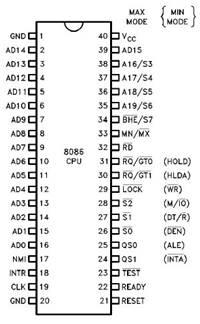

Схема цоколевки микроконтроллера i8086 приведена на рис.2

Рис. 2 Условное графическое обозначение микроконтроллера i8086

Шестнадцатиразрядный однокристальный МП выполняющий около 2 млн. операций в секунду. Синхронизируется тактовой частотой 25 МГЦ. Имеет 20-ти разрядную шину адреса, что позволяет обеспечить прямую адресацию 1 Мбайт внешней памяти. Область адресного пространства памяти разбита на сегменты по 64 Кб. Такая организация памяти обеспечивает удобный механизм вычисления физических адресов. ША и ШД мультиплексированы. При организации вычислительных систем их нужно разделить (регистры-защелки). МП может обращаться как к памяти, так и к внешним устройствам. При обращении к внешним устройствам используются 16 младших линий ША. Следовательно можно подключить 64 К 8-битных внешних устройств, либо 32 К 16-ти разрядных. МП имеет многоуровневую систему прерываний: 256 векторов прерываний. Данный МП является дальнейшим совершенствованием К580ВМ80. Система команд сходна, но более расширена. Программное обеспечение легко переводится с одного МП на другой.

Наименование выводов i8086:

NMI – запрос на немаскируемое прерывание

INTR – запрос на маскируемое прерывание

CLK – выход ГТИ для управления памятью

RESET – сигнал системного сброса

READY – выход готовности генератора

TEST – проверочный вход, используется в команде WAIT для организации холостых тактов: «1» - МП выполняет «0», с периодичностью 5 Т проверяет состояние этого сигнала

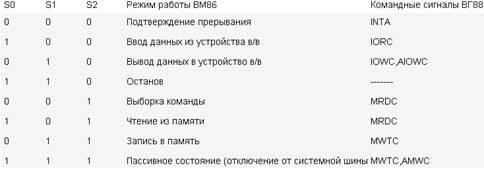

S0-S2 – предназначены для подключения к центральному микропроцессору

LOCK – вход запрета освобождения системной шины: «1» - арбитру запрещается освобождать системную шину, не зависимо от его приоритета

RQ/GT – обеспечивает доступ к линии связи только одному МП. Выходы другого в этот момент находятся в 3-м состоянии. Дешифратор адреса определяет адрес всей конкретной схемы

RD – чтение

MN/MX – минимальный / максимальный режимы, определяющие конфигурацию вычислительной системы. MN- ограничение объема памяти и т.д.

GND- линия заземления

AD0-AD15 – мультиплексированная шина адреса/ данных

A16/S3-A19/S6 – мультиплексированные линии адреса состояния

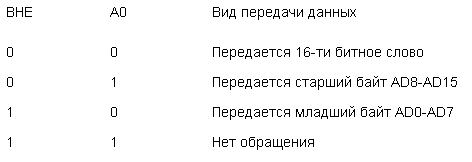

BHE – разрешение старшего байта. Работает совместно с сигналом А0, обеспечивая механизм передачи информации по ШД

DEN - строб сопровождения данных для фиксации в регистры-защелки

ALE – строб сопровождения адреса в регистр-защелку

INTA – системный сигнал подтверждения прерывания

Vcc – вывод источника питания

Основные технические характеристики:

· Тактовая частота От 0 до 5 МГц (i8086)

· Разрядность регистров: 16 бит

· Разрядность шины данных: 16 бит

· Разрядность шины адреса: 20 бит

· Объём адресуемой памяти: 1 Мбайт

· Количество транзисторов: 29 000

· Техпроцесс (нм): 3000 (3 мкм)

· Площадь кристалла (кв. мм): ~30 (по другим данным, 16 мм²)

· Максимальное тепловыделение: 1,75 Вт

· Разъём: нет (микросхема припаивалась к плате)

· Поддерживаемые технологии: 98 инструкций

· Диапазон напряжения питания:

- от 2,7 до 5,0 В (i8086)

· Корпус: 40-контактный керамический DIP

2. Разработка и описание схемы

2.1 Процессорный блок

Процессорный блок состоит из микроконтроллера i8086, регистра защелки младшей части адреса RG. Адрес формируется на выходе портов РА – младшая часть adr(0..7) на внутренней шине AdrDat, которая попадает на системную шину адреса после регистра защелки Adr, и РС – старшая часть, которая непосредственно подается на системную Adr - разряды adr(8..15). Обмен данными с памятью и внешними устройствами, осуществляется как по внутренней шине Dat, которая совмещена с шиной младшей части адреса и подключена к порту РА dat(0..7)=adr(0..7), так и по порту РС.

Сигнал ALE является сигналом защелкивания младшей части адреса в регистр RG.

РD2, РD3 – линии приема запроса на прерывание по вводу данных от внешнего устройства, РD6 и РD7 – линии сигналов записи и чтения.

2.2 Расчет ОЗУ

Исходные данные:

Количество ячеек внешнего ОЗУ NОЗУ

– 0,512 Кбайт

Количество входов параллельного интерфейса:

режим 0 – 8

Количество выходов параллельного интерфейса:

режим 0 – 16

Входные токи:

при логическом 0, IIL

– 3,2 мА

при логической 1, IIH

– 2 мА

Входная емкость логических схем нагрузки, СI

– 5 пФ

Монтажные емкости всех цепей (См

= 20 пФ).

Согласно заданию количество ячеек памяти ОЗУ составляет NОЗУ.

Разрядность ОЗУ nОЗУ

должна соответствовать разрядности обработки данных ЦП.

Информационная емкость СОЗУ

определяется по формуле:

Необходимое быстродействие ОЗУ определяется по временным диаграммам ЦП. Для МК i8086 время цикла записи (чтения) tС

равно 3ТМТ

, где ТМТ

- длительность машинного такта.

При частоте кварцевого резонатора fтг

= 10 МГц время Тмт

= 100 нс.

Время цикла микросхемы памяти tcy

должно удовлетворять неравенству:

В качестве микросхемы ОЗУ выберем К537РУ17, поскольку она будет (прогнозируемо) наименее избыточна для данного случая. Для данной микросхемы памяти . .

Рассчитаем число БИС ОЗУ в ряду матрицы:

где nБИС

- разрядность выбранной микросхемы памяти. Квадратные скобки здесь и в дальнейшем показывают, что результат необходимо округлить до большего значения.

Определим число разрядов матрицы:

где NБИС

- количество ячеек памяти выбранной микросхемы памяти.

Общее число БИС ОЗУ равно

Таким образом, число корпусов ОЗУ = 2.

Определяем токовую IDL

и IDH

и емкостную СD

нагрузки для схем ввода информации в ОЗУ по формулам:

IDL

= mc

* IIDL

= 2 * 3,2 = 6,4 мА

IDH

= mc

* IIDH

= 2 * 2 = 4 мА

CD

= mc

* CID

+ Cm

= 2 * 5 + 20 = 30 пФ

где IIDL

, IIDH

- входные токи логического 0 и логической 1 по информационным цепям выбранной БИС ОЗУ. CID

- входная емкость по информационному входу БИС ОЗУ.

Определяем токи нагрузки и емкостную нагрузку для схем ввода адреса по адресным цепям БИС ОЗУ по формулам:

IAL

= m * IIAL

= 2 * 3,2 = 6,4 мА

IAH

= m * IIAH

= 2 * 2 = 4 мА

CA

= m * CIA

+ Cm

= 2 * 5 + 20 = 30 пФ

где IIАL

, IIAH

- входные токи логического 0 и логической 1 по адресным цепям выбранной БИС ОЗУ. CIА

- входная емкость по адресному входу БИС ОЗУ.

Определяем токи нагрузки ICSL

и ICSH

и величину емкостной нагрузки СCS

по цепям выбора микросхем (CS) по формулам:

ICSL

= mp

* IICSL

= 1 * 3,2 = 3,2 мА

ICSH

= mp

* IICSH

= 1 * 2 = 2 мА

CCS

= mp

* CICS

+ Cm

= 1 * 5 + 20 = 25 пФ

где IICSL

, IICSH

- входные токи логического 0 и логической 1 по цепям выбора (CS) БИС ОЗУ. CСS

- входная емкость по цепям выбора (CS) БИС ОЗУ.

Рис. 3 Условное графическое обозначение ОЗУ К537РУ17

Наименование выводов:

A0 ÷ A12 – адресные входы.

W/R – запись/чтение.

CS1, CS2 – chip select, чип выбора.

CEO – разрешающий выход.

D0 ÷ D7 – шина данных ввода/вывода.

ОЗУ представляет собой статическое асинхронное оперативное запоминающее устройство.

Режимы работы:

| W/R |

CS1 |

CS2 |

OE |

A0..12 |

D0..7 |

Режим |

| Х |

Н |

X |

X |

Адрес |

Данные |

Хранение |

| Х |

Х |

L |

Х |

Хранение |

| Н |

L |

Н |

H |

Запрет выхода |

| Н |

L |

H |

L |

Чтение |

| L |

L |

Н |

Н |

Запись |

| L |

L |

Н |

L |

Запись |

2.3 Описание адаптера параллельного интерфейса

Адаптер параллельного интерфейса служит для расширения разрядности шины данных, а также приводит к повышению нагрузочной способности.

Адаптер параллельного интерфейса i8255 имеет три восьмиразрядных порта А, В и С с 3-м состоянием. Причем порт С разделен на две тетрады. Все три порта могут быть запрограммированы на ввод или вывод, причем каждая тетрада порта С может быть запрограммирована раздельно. Данные поступают в АПИ через шину данных D0…D7. С помощью сигнала CS осуществляется выбор кристалла, если сюда поступает низкий уровень сигнала, то порты будут установлены в 3-е состояние. А1, А0 – младшие разряды адреса, они служат для адресации внутренних регистров адаптера. Если количество линий ввода и вывода превышает возможности адаптера, то следует применить несколько адаптеров.

Рис. 4 Условное графическое обозначение АПИ i8255

Наименование выводов:

D0 ÷ D7 – шина данных.

CS – выбор кристалла, активный 0 – адаптер подключен к PPI, если 1 – адаптер имеет третье высокоимпедансное состояние.

A0, A1 – младшие разряды адреса, служат для адресации внешних регистров адаптера.

WR – запись, поступает от МК.

RD – чтение, поступает от МК.

RESET – системный сброс.

PA0 ÷ PA7 – 8-разрядный двунаправленный порт A с третьим состоянием.

PB0 ÷ PB7 – 8-разрядный двунаправленный порт B с третьим состоянием.

PB0 ÷ PB7 – разделен на 2 части, 8-разрядный двунаправленный порт С с третьим состоянием.

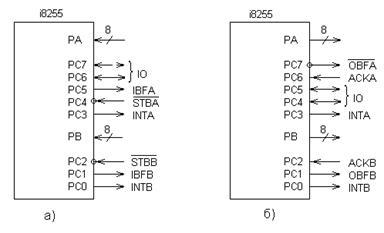

Адаптер имеет три режима роботы. Рассмотрим некоторые особенности каждого из режимов:

Режим 0

применяется в программно-управляемом вводе-выводе с медленно действующими периферийными устройствами. В режиме 0 базового ввода-вывода могут работать все три порта, причем порт С разделяется на два независимых четырехбитных порта.

Режим 1

- стробируемый ввод-вывод. Он предназначен для однонаправленных передач данных, инициируемых прерываниями. Собственно передача слов данных осуществляется через порты А и В, а шесть линий порта С используются для управления обменом. Данный режим предоставляет пользователю следующие возможности: запрограммировать один или два параллельных порта с линиями квитирования и прерывания, каждый из которых может работать на ввод или вывод; при использовании только одного порта остальные 13 линий запрограммировать в режиме 0; при определении двух портов в режиме 1 оставшиеся две линии порта С использовать для ввода или вывода в режиме 0. На рис. 5. приведено расположение линий порта С при вводе информации (рис. 5, а) и при выводе информации (рис. 5, б) через порты А и В, где

IO - ввод или вывод в зависимости от значения бита D4 слова приказа (СП).

IBF - ввод в буфер. Устанавливается в 1 и поддерживается в течении всего времени от записи данных (в А или В) до момента их чтения из МП.

STB - строб приема. По данному сигналу информация записывается в выбранный порт.

INT - запрос прерывания. Информирует МП о готовности данных к выводу. Подается на вход запрос прерывания ЦП.

OBF - выходной порт полон. Сигнализирует ВУ, что данные находятся в порту А или В.

ACK - подтверждение. ВУ подтверждает прием данных.

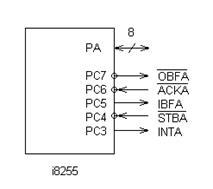

Режим 2

- совместный ввод - вывод с квитированием. Осуществляется только по порту А, при этом порт А используется для двунаправленной передачи данных, канал С - выполняет функции управления (квитирования) и прерываний. Порт В можно запрограммировать на ввод или вывод в режимах 0 или 1.

На рис. 6. Приведено расположение линий порта С в режиме 2.

Рис. 5 Распределение линий порта С: а) при вводе информации в порты А и В; б) при выводе информации.

Рис. 6 Расположение линий порта С в режиме 2.

2.4 Программирование адаптера параллельного интерфейса

Программирование адаптера заключается в загрузке слова приказа (СП) в регистр управляющего слова ICW1.

Формат данного регистра представлен ниже

D7 D0

Описание битов:

· D7 – признак ICW1

· D6, D5 – режим работы для группы А

· D4 – ввод/вывод по порту А (вывод – 0, ввод – 1)

· D3 – ввод/вывод по порту C4…7 (вывод – 0, ввод – 1)

· D2 – режим работы для группы В

· D1 – ввод/вывод по порту B (вывод – 0, ввод – 1)

· D0 – ввод/вывод по порту C0…3 (вывод – 0, ввод – 1)

В данном случае слово приказа можно составить двумя способами:

ICW1=10010010=92h

D7 D0

- в режиме 0 задействовано всего 16 входов – 8 входов порта А и 8 входов порта В, которые работают на ввод;

- в режиме 0 задействовано всего 8 выходов – 8 выходов порта С, которые работают на вывод.

Напишем программу для инициализации АПИ в первом случае:

C55 equ Е002h

B55 equ Е001h

A55 equ Е000h

RUS equ Е003h

ICW1 equ 92h

LDI DPTR, #RUS ;адрес регистра управляющего слова ->регистр

;указатель данных

LDI A,#ICW1

LDI @DPTR,A ;загрузка слова-приказа в РУС

Выводы

В ходе выполнения работы была разработана система обработки данных с заданными параметрами ОЗУ и адаптера параллельного интерфейса. Были изучены основные способы разработки устройств обработки информации, базовые методы расчета количества микросхем ОЗУ для обеспечения необходимого количества ячеек памяти микроконтроллеру, способы планирования и синтеза схем на основе микроконтроллеров.

|