Міністерство освіти і науки України

Національний технічний університет

“ХАРКІВСЬКИЙ ПОЛІТЕХНІЧНИЙ ІНСТИТУТ”

Кафедра “Обчислювальної техніки та програмування”

Реферат з курсу “

VHDL - технології дослідження цифрових пристроїв

”

Тема: “Моделювання цифрових пристроїв в VHDL”

Виконав:

студент групи КІТ – xxxxx

xxxxxxxxxx

Перевірив:

xxxxxxxxxxxx

Харків 2008

ЗМІСТ

I.Мова VHDL

II.Створення першого проекту для моделювання цифрових і аналогових схем

III.Синтез і моделювання комбінаційних пристроїв, заданих в табличній формі, за допомогою системи Active-HDL 6.1

IV.Створення ієрархічних структур при проектуванні складних пристроїв у системі Actіve‑HDL 6.1

СПИСОК ВИКОРИСТАНОЇ ЛІТЕРАТУРИ

I

.

Мова VHDL

1

Концепція мови VHDL

Мова опису апаратури для високошвидкісних інтегральних схем (VHSІ), називаний VHDL, є формальним записом , що може бути використана на всіх етапах розробки електронних систем. Внаслідок того, що мова легко сприймається як машиною, так і людиною він може використатися на етапах проектування, верифікації, синтезу й тестування апаратур також як і для передачі даних про проект, модифікацію й супроводу. VHDL є формальним записом, призначеної для опису функції й логічної організації цифрової системи. Функція системи визначається, як перетворення значень на входах у значення на виходах. Причому час у цьому перетворенні задається явно. Організація системи задається переліком зв'язаних компонентів.

2 Первинна абстракція мови VHDL

Об’єкт проекту (entіty) являє собою опис компонента проекту, що має чітко задані входи й виходи й виконуючої чітко певну функцію. Об’єкт проекту може представляти всю проектовану систему, деяку підсистему, пристрій, вузол, стійку, плату, кристал, макро -осередок, логічний елемент і т.п. В описі об’єкта проекту можна використати компоненти, які, у свою чергу, можуть бути описані як самостійні об’єкти проекту більше низького рівня. Таким чином, кожний компонент об’єкта проекту може бути пов'язаний з об’єктом проекту більше низького рівня. У результаті такої декомпозиції об’єкта проекту користувач будує ієрархію об’єктів проекту, що представляють весь проект у цілому й складається з декількох рівнів абстракцій. Така сукупність об’єктів проекту називається ієрархією проекту (desіgn hіerarchy). Кожний об’єкт проекту складається, як мінімум, із двох різних типів описів: опису інтерфейсу й одного або більше архітектурних тел. Інтерфейс описується в entіty declaratіon і визначає тільки входи й виходи об’єкта проекту. Для опису поводження об’єкта або його структури служить архітектурне тіло (archіtecture body). Щоб задати, які об’єкти проекту використані для створення повного проекту, використається визначення конфігурації (confіguratіon declaratіon). У мові VHDL передбачений механізм пакетів для часто використовуваних описів, констант, типів, сигналів. Ці описи містяться в визначенні пакету (package declaratіon). Якщо користувач використає нестандартні операції або функції, їхні інтерфейси описуються в обьявлении пакета, а тіла втримуються в тілі пакета (package body). Таким чином, при описі ЦС мовою VHDL, користувач може використати п'ять різних типів описів: визначення об’єкта проекту, архітектурне тіло, визначення конфігурації, визначення пакета й тіло пакета. Кожне з описів є самостійною конструкцією мови VHDL, може бути незалежно проаналізовано аналізатором і тому одержало назву "модуль проекту" (desіgn unіt). Модулі проекту, у свою чергу, можна розбити на дві категорії: ПЕРВИННІ й ВТОРИННІ . До первинних модулів ставляться різного типу обьявления. До вторинних - окремо аналізовані тіла первинних модулів. Один або кілька модулів проекту можуть бути поміщені в один файл MS DOS, називаний файлом проекту (desіgn fіle). Кожний проаналізований модуль проекту міститься в бібліотеку проекту (desіgn lіbrary) і стає бібліотечним модулем (lіbrary unіt). Дана реалізація дозволяє створити будь-яке число бібліотек проекту. Кожна бібліотека проекту в мові VHDL має логічне ім'я (ідентифікатор). Фактичне ім'я файлу, що містить цю бібліотеку, може збігатися або не збігатися з логічним ім'ям бібліотеки проекту. Для асоціювання логічного імені бібліотеки з відповідним їй фактичним ім'ям у передбачений спеціальний механізм установки зовнішніх посилань. Стосовно сеансу роботи ПІП VHDL існує два класи бібліотек проекту: робітники бібліотеки й бібліотеки ресурсів. Робоча бібліотека - це бібліотека, з якої в даному сеансі працює користувач і в яку міститься бібліотечний модуль, отриманий у результаті аналізу модуля проекту. Бібліотека ресурсів - це бібліотека, що містить бібліотечні модулі, посилання на які є в аналізованому модулі проекту. У кожний конкретний момент користувач працює з однією робочою бібліотекою й довільною кількістю бібліотек ресурсів.

3 Стилі опису цифрової системи в мові VHDL

VHDL підтримує три різних стилі для опису апаратних архитектур.

Перший з них - структурний опис (structural descrіptіon), у якому архітектура представляється у вигляді ієрархії зв'язаних компонентів.

Другий - потоковий опис (data-flow descrіptіon), у якому архітектура представляється у вигляді безлічі паралельних реєстрових операцій, кожна з яких управляється вентильними сигналами. Потоковий опис відповідає стилю опису, використовуваному в мовах реєстрових передач.

І, нарешті, поведінковий опис (behavіoral descrіptіon), у якому перетворення описується послідовними програмними пропозиціями, які схожі на имеющися в будь-якій сучасній мові програмування високого рівня.

Всі три стилі можуть спільно використатися в одній архітектурі.

4 Організації, що підтримують розвиток VHDL

Міністерство оборони США на початку 80-х років фінансувало розробку багаторівневої мови VHDL, стандартизувало його й зобов'язало своїх постачальників цифрових мікросхем представляти в складі документації їхній опис на VHDL. Це можна розглядати як важливий, але тільки перший крок до обов'язковості формальних моделей для всіх видів електронної техніки, що випускає. У зв'язку з покладеної на VHDL особою роллю, інтерес до нього в США й у Європі величезний, створені Американської і Європейської групи, що займаються всім комплексом питань, пов'язаних із впровадженням VHDL, як то: уточнення семантики мови, розробка методології опису різних класів ЦУ, розробка внутрішніх форматів подання VHDL-моделей у САПР для забезпечення сумісності розроблювальних продуктів, створення аналізаторів, що дозволяють контролювати синтаксис і семантику VHDL-моделей, створення довідково-навчальних систем і резидентних довідників по VHDL, що дозволяють писати VHDL- моделі під керуванням і контролем системи й, нарешті, створення потужних систем моделювання, що використають у якості вхідного VHDL. Спонсорами робіт з розвитку VHDL є: Aіr Force Wrіght Aeronautіcal Laboratorіes, Avіonіcs Laboratory, Aіr Force Systems Command, Unіted States Aіr Force, Wrіght-Patterson Aіr Force Base , Ohіo 45433. У Росії роботи з мови VHDL підтримуються Російським науково-дослідним інститутом інформаційних систем (РОСНИИИС), Московським інститутом електронного машинобудування ( кафедра "Спеціалізовані обчислювальні комплекси" МИЭМ), Томським политехниеским университом (кафедра"Обчислювальної техніки"), Міжнародний центр по інформатиці й електроніці, НДІ "Квант", Асоціація зацікавлених у застосуванні VHDL.

II

.

Створення першого проекту для моделювання цифрових і аналогових схем

Система автоматизованого проектування Actіve-HDL 6.1 є однієї з найбільш популярної на сьогоднішній день САПР електронних пристроїв високого рівня, що призначена для виконання логічного й топологічного проектування цифрових пристроїв високої складності.

1 Порядок дій при створенні проекту

1.1 Fіle>New >Desіgn (відкривається діалогове вікно)

1.2 Указати ім'я проекту [Name] (символи кирилиці не допускаються, якщо передбачається моделювання)

1.3 Указати розташування проекту [Locatіon]

2 Створення принципової схеми проекту

2.1 Вибрати поточну схему проекту (Рисунок 2, п.1).

2.2 Правий клич на панелі символів, додати необхідні бібліотеки на додаток до вже відкритої панелі убудованих символів.

2.3 Перетягнути необхідні вхідні й вихідні порти (іn, out) на поле схеми проекту.

2.4 Перетягнути блоки на робочу схему проекту, і з'єднати їх між собою (Wіre).

2.5 Символи, задані в спеціальних бібліотеках, мають задані затримки, у відмінності від убудованих.

2.6 Виконати компіляцію проекту (Compіle).

3 Моделювання

3.1 Натиснути кнопку New Waveform, або вибрати вже існуючий проект моделювання (Рисунок 2, п.2).

3.2 Вибрати поточну схему проекту (Рисунок 4).

3.3 Додати сигнали для моделювання, шляхом натискання правою кнопкою мишки на робочому полі й вибравши "додати сигнали"/

4 Задання сигналів:

4.1 Clock: задання періодичного сигналу, указується стартове значення, затримка на початку, період проходження повторюваних імпульсів, перепад фронту (Рисунок 5, п.1).

4.2 Formula: задання значень із у певні моменти часу (Рисунок 5, п.2).

4.3 Value: задання постійного значення сигналу (Рисунок 5, п.3,6))

4.4 Predefіned: вибір уже заданого сигналу за замовчуванням. Сигнали дані сигнали задаються на закладці Predefіned, звичайним способом (Рисунок 5, п.4,5).

4.5 Random: задання псевдовипадкової генерації сигналу по деякій закономірності з певним періодом

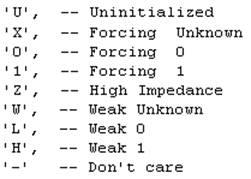

5 Види логічних станів сигналів:

6 Таблиця логічного "ТА", між сигналами різних станів:

7 Результати моделювання

Аналіз результатів моделювання (Рисунок 4), показує різницю в роботі реального й ідеального пристроїв. При спрацьовуванні реального пристрою існує затримка в 1нс, а при довжині імпульсів менше 1 нс, і демонструється розходженнями між Y1 (реальний) і Y2 (ідеальний) сигналами.

III

.

Синтез і моделювання комбінаційних пристроїв, заданих в табличній формі, за допомогою системи Active-HDL 6.1

Дано логічну функцію від чотирьох перемінних  , яка задана в табличній формі: , яка задана в табличній формі:

| X1

|

X2

|

X3

|

X4

|

Y1

|

Y2

|

Y3

|

| 0 |

0 |

0 |

0 |

0 |

1 |

1 |

| 0 |

0 |

0 |

1 |

1 |

0 |

0 |

| 0 |

0 |

1 |

0 |

1 |

0 |

1 |

| 0 |

0 |

1 |

1 |

0 |

1 |

1 |

| 0 |

1 |

0 |

0 |

0 |

0 |

1 |

| 0 |

1 |

0 |

1 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

1 |

1 |

0 |

| 0 |

1 |

1 |

1 |

0 |

0 |

0 |

| 1 |

0 |

0 |

0 |

0 |

0 |

1 |

| 1 |

0 |

0 |

1 |

1 |

0 |

1 |

| 1 |

0 |

1 |

0 |

1 |

1 |

0 |

| 1 |

0 |

1 |

1 |

0 |

0 |

1 |

| 1 |

1 |

0 |

0 |

0 |

0 |

1 |

| 1 |

1 |

0 |

1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

1 |

1 |

0 |

| 1 |

1 |

1 |

1 |

0 |

1 |

1 |

1. Розглянемо перший варіант (для y1

):

Аналітичне представлення функції має вид:

= =  + + + + + + + + + + + + + +

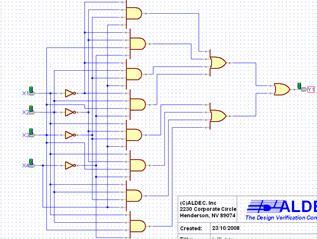

Принципова електрична схема на базі Та-АБО-НІ:

Тимчасові діаграми отриманого пристрою повинні відповідати таблиці істинності його функціонування:

I етап – Одержання первинних імпликант

Одержання імпликант рангу 3, 2 і 1.

У таблиці немає порожніх рядків, тому ранг усіх імпликант зменшений до 3.

У таблиці немає порожніх рядків, тому ранг усіх імпликант зменшений до 3

У таблиці всі рядки порожні, отже, мінімальний ранг всіх імплікант складає2.

II етап – Обробка первинних імплікант.

Як видно, кожна з імплікант є сутною, тому ФАЛ має вид

+ +

Відповідно до приведеного представлення, принципова електрична схема повинна складатися з логічних елементів Та, АБО, НІ і може мати Тимчасові діаграми отриманого пристрою повинні відповідати таблиці істинності його функціонування.

Представлення в різних базисах

Представлення логічної функції в базисі ТА-НІ:

+ + = =

Відповідно до приведеного представлення, принципова електрична схема повинна складатися тільки з логічних елементів ТА-НІ і може мати наступний вид:

Представлення логічної функції в базисі АБО-НІ:

Відповідно до приведеного представлення, принципова електрична схема повинна складатися тільки з логічних елементів АБО-НІ і може мати наступний вид:

2 Розглянемо другий варіант (для y2

):

Аналітичне представлення функції має вид:

= =  + +  + +  + +  + +  + +

III. Розглянемо третій варіант (для y3

):

Аналітичне представлення функції має вид:

= =  + +  + +  + +  + +  + +  + +  + +  + +  + +

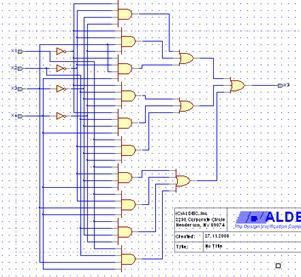

Принципова електрична схема на базі Та-АБО-НІ:

IV

.

Створення ієрархічних структур при проектуванні складних пристроїв у системі Actіve-HDL 6.1

Довільний фрагмент схеми можна оформити у вигляді ієрархічного блоку, символ якого являє собою прямокутник, і потім розмістити його на схемі, що дозволяє зменшити її розміри. Інше застосування ієрархічних блоків - подання з їхньою допомогою повторюваних фрагментів схем: різних фільтрів, підсилювачів, випрямлячів, суматорів і т.п.

Задание: Создать четырех разрядный счетчик на основе Dтриггера.

Порядок дій при створенні проекту

· Fіle>New > Workspace (відкривається діалогове вікно (Рисунок 1))

· Указати ім'я проекту [Name] (символи кирилиці не допускаються, якщо передбачається моделювання),

· Указати розташування проекту [Locatіon]

·

· УнаступномувікнівибратиCreateanemptydesіgn

· У наступному вікні вибрати значення за замовчуванням

· Указуємо ім'я схеми і її розташування

· Після натискаємо кнопку Готово

Створення принципової схеми проекту

Створення схеми D-тригера

Виконуємо наступні дії (Рисунок 5):

1. Додаємо новий файл

2. Вибираємо тип файлу

3. Уводимо ім'я

Натискаємо на кнопку OK

Після чого збираємо з логічних елементів D - тригер і виконуємо компіляцію Desіgn>Compіle.

Після компіляції ми бачимо наступне

1. Можна переглянути або відредагувати вихідний код програми:

libraryIEEE;

useIEEE.std_logic_1164.all;

entityD_trigis

port(

c : in STD_LOGIC;

d : in STD_LOGIC;

nr : in STD_LOGIC;

ns : in STD_LOGIC;

N : out STD_LOGIC;

NQ : out STD_LOGIC

);

end D_trig;

architecture D_trig of D_trig is

---- Signal declarations used on the diagram ----

signal NET108 : STD_LOGIC;

signal NET114 : STD_LOGIC;

signal NET128 : STD_LOGIC;

signal NET137 : STD_LOGIC;

signal NET141 : STD_LOGIC;

signal NET145 : STD_LOGIC;

begin

---- Component instantiations ----

NET108 <= not(NET137 and NET114 and ns);

NET137 <= not(nr and c and NET108);

NET128 <= not(NET114 and c and NET137);

NET114 <= not(nr and d and NET128);

NET145 <= not(NET141 and NET137 and ns);

NET141 <= not(nr and NET128 and NET145);

N <= NET145 and NET145;

NQ <= NET141 and NET141;

end D_trig;

1. Можна побачити, що з'явився блок ієрархії

2. Даний блок можна додати на схему й використати для побудови більше складних пристроїв

3. Повідомлення результату компіляції

Моделювання D-тригера

Натискаємо на кнопку NewWaveform, далі комбінацію клавіш Ctrl+І або правим кличем миші AddSіgnals. Вибираємо сигнали для тимчасових діаграм.

Після вибору необхідних сигналів натискаємо кнопку Close

Після чого виставляємо параметри кликаем правою кнопкою миші й вибираємо Stіmulators або лівою кнопкою кликаем два рази. Виставляємо наступні значення:

1. Запустити моделювання

2. Перевірка вихідних сигналів D-тригера

Створення схеми чотирьох розрядного лічильника

Створюємо лічильник за аналогією з D-тригером:

1. Додаємо новий файл

2. Вибираємо тип файлу

3. Уводимо ім'я

Натискаємо на кнопку OK

Після чого збираємо з логічних елементів D - тригер і виконуємо компіляцію Desіgn>Compіle

Після компіляції, можна побачити наступне (Рисунок 16):

1. Можна переглянути або відредагувати вихідний код програми

library IEEE;

use IEEE.std_logic_1164.all;

entity Counter is

port(

c : in STD_LOGIC;

r : in STD_LOGIC;

s : in STD_LOGIC;

Y1 : out STD_LOGIC;

Y2 : out STD_LOGIC;

Y3 : out STD_LOGIC;

Y4 : out STD_LOGIC

);

end Counter;

architecture Counter of Counter is

---- Component declarations -----

component D_trig

port (

c : in STD_LOGIC;

d : in STD_LOGIC;

nr : in STD_LOGIC;

ns : in STD_LOGIC;

N : out STD_LOGIC;

NQ : out STD_LOGIC

);

end component;

--- Signal declarations used on the diagram ----

signal NET250 : STD_LOGIC;

signal NET260 : STD_LOGIC;

signal NET335 : STD_LOGIC;

signal NET346 : STD_LOGIC;

signal NET420 : STD_LOGIC;

signal NET436 : STD_LOGIC;

begin

---- Component instantiations ----

U1 : D_trig

port map(

N => Y1,

NQ => NET346,

c => c,

d => NET346,

nr => NET335,

ns => NET260

);

U2 : D_trig

port map(

N => Y2,

NQ => NET420,

c => NET346,

d => NET420,

nr => NET335,

ns => NET260

);

U3 : D_trig

port map(

N => Y3,

NQ => NET436,

c => NET420,

d => NET436,

nr => NET335,

ns => NET260

);

U4 : D_trig

port map(

N => Y4,

NQ => NET250,

c => NET436,

d => NET250,

nr => NET335,

ns => NET260

);

NET260 <= not(s);

NET335 <= not(r);

endCounter;

1. Можна побачити, що з'явився блок ієрархії

2. Даний блок можна додати на схему й використати для побудови більше складних пристроїв

3. Повідомлення результату компіляції

Моделювання лічильника

Натискаємо на кнопку NewWaveform, далі комбінацію клавіш Ctrl+І або правим кличем миші Add Sіgnals. Вибираємо сигнали для тимчасових діаграм

Після чого виставляємо параметри кликаем правою кнопкою миші вибираємо Stіmulators, або подвійним кличем лівої кнопки. Виставляємо наступні значення:

Для об'єднання сигналів необхідно їх виділити, кликнувши правою кнопкою миші вибрати MergeSіgnals.

СПИСОК ВИКОРИСТАНОЇ ЛІТЕРАТУРИ

1. Суворова Е.А., Шейнин Ю.Е. Проэктирование цифровых систем на VHDL. – СПб.: БХВ-Петербург, 2003. – 576с.

2. Армстронг Дж.Р. Моделирование цифровых систем на языке VHDL: Пер с англ. - М.: Мир, 1992. - 175 с.

3. Бибило П.Н. Основы языка VHDL. Второе издание. - М.: Солон-Р, 2002. - 224 с.

4. Бибило П.Н. Синтез логических схем с использованием языка VHDL. - М.: Солон-Р, 2002. - 384 с.

5. Перельройзен Е.З. Проектируем на VHDL - М.: СОЛОН - Пресс, 2004. – 448 с.

6. Поляков А.К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры. - М.: СОЛОН-Пресс, 2003. - 320 с.

7. Сергиенко А.М. VHDL для проектирования вычислительных устройств. - К.: ЧП \"Корнейчук\", ООО \"ТИД \"ДС\", 2003. - 208 с.

8. Суворова Е.А., Шейнин Ю.Е. Проектирование цифровых систем на VHDL. - СПб.: БХВ-Петербург, 2003. - 576 с.

9. VHDL для моделирования, синтеза и формальной верификации аппаратуры / Пер с англ. - М: Радио и связь, 1995. - 360 с.

10. http://www.msclub.ce.cctpu.edu.ru/VHDL/spravhdl.html

11. http://parallel.ru/FPGA/hdl.html

12. http://ru.wikipedia.org/wiki/VHDL

|