|

Министерство образования Российской Федерации

Уральский государственный университет – УПИ

Кафедра «Автоматики и информационных технологий»

РЕГИСТРОВАЯ ПАМЯТЬ ТИПА "МАГАЗИН"

Курсовая работа по дисциплине

«Схемотехника ЭВМ»

Пояснительная записка

Студент группы

Преподаватель

2005

Содержание

1. Задание на курсовой проект

2. Введение

3. Общий принцип работы памяти типа "очередь"

5. Функциональная схема блока управления

5.1 Блок формирования адреса

5.2 Блок дешифрирования адреса

5.3 Блок проверки заполнения памяти

5.4 Инкрементор

6. Функциональная схема блока регистров

7. Параметры некоторых микросхем

7.1 Счетчики

7.2 Дешифраторы

7.3 Регистры

7.4 Компаратор

8. Принципиальная схема устройства

8.1 Перечень элементов

8.2 Питание микросхем

9. Временные диаграммы

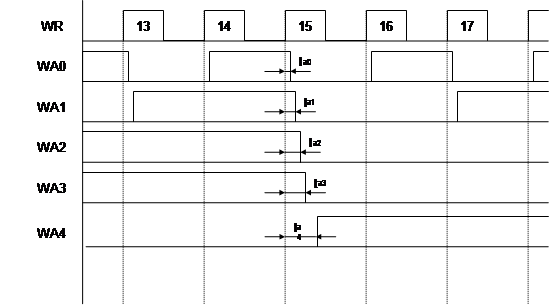

9.1 Временная диаграмма блока формирования адреса

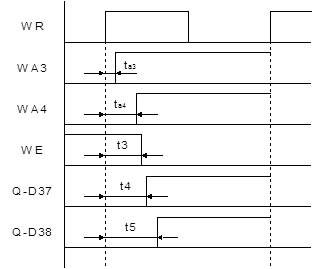

9.2 Временная диаграмма блока дешифрирования адреса

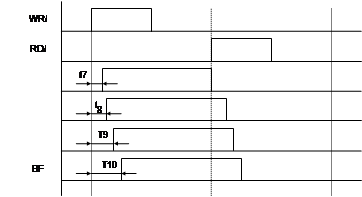

9.3 Временная диаграмма блока проверки заполнения памяти

9.4 Временная диаграмма блока регистров

10. Расчет параметров устройства

10.1 Токи и потенциалы

10.2 Нагрузка

10.3 Потребляемая мощность

11. Заключение

Библиографический список

Разработать структурную, функциональную и принципиальную схемы для устройства регистровой памяти типа "магазин".

Выполнить необходимые расчеты для обеспечения требуемых токов и потенциалов для используемых элементов, определить временные соотношения и потребляемую мощность.

Объем памяти – 256 бит (32x8).

Элементная база КМОП.

В цифровой аппаратуре широко используются небольшие вспомогательные запоминающие устройства с неявно выраженной адресацией, служащие для хранения очередей и называемые иногда буферами данных. Часто их строят на основе регистровой памяти.

Часто используемым в цифровой технике буфером является буфер типа «магазин», или стек, или LIFO. В отличии от нормальной очереди здесь в качестве первого кандидата на обслуживание выбирается то слово, которое встало в очередь последним. По такому закону заряжается патронами и освобождается в процессе работы магазин автоматического оружия, откуда и произошло одно из названий. Стековые структуры данных возникают в цифровых устройствах, когда процесс выполнения менее срочного задания прерывается более срочным и все данные, связанные с прерванной работой, засылаются на временное хранение в буфер типа «магазин». Выполнение срочного задания может быть в свою очередь прервано поступлением сверхсрочного и т.д.- и в стеке по мере погружения туда (сверху) новых и новых данных формируется очередь слов, стековый порядок извлечения которых (тоже сверху) соответствует правильной по рангу срочности очередности их обработки.

Рис. 1. Буфер типа "Магазин"

Счетчик должен быть реверсивным, т.е. уметь прибавлять 1, когда поступает команда «Заслать в стек» и вычитать 1 при команде «Извлечь из стека». При этом адрес, по которому производится засылка в стек, всегда на единицу больше адреса, по которому выполняется чтение из стека. Постоянный сдвиг на единицу адреса записи относительно адреса чтения выполняет инкрементор. Стек имеет два особых состояния: «буфер пуст» и «буфер полон». Обнаруживаются они непосредственно по нулевому и по максимальному возможному (все единицы) состоянием счетчика адреса. 4. Общая структурная схема

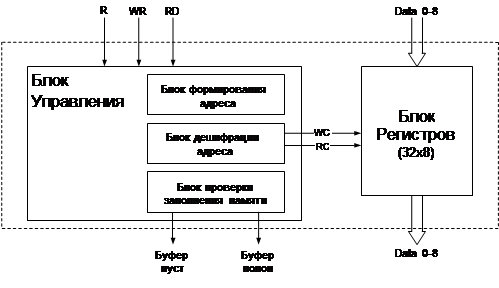

Структурная схема устройства регистровой памяти типа "магазин" представлена на рис. 2

Рис. 2. Структурная схема

Регистровая память типа "магазин" состоит из двух блоков. Блок управления предназначен для вычислений адресов записи и считывания, проверки буфера на переполнение, обнуления памяти и синхронизации с потоком данных. Входными сигналами для блока управления являются сигнал обнуления памяти, сигнал разрешения записи в память, сигнал разрешения чтения из памяти.

Блок управления в свою очередь состоит из блока формирования адреса, блока дешифрации адреса и блока проверки заполнения памяти.

Блок регистров представляет собой обыкновенный регистровый файл.

Принцип работы устройства заключается в следующем. Сигнал записи в память поступает в блок управления, по его приходу в блоке формирования адреса формируется адрес записи путем прибавления единицы к текущему адресу. Сформированный адрес поступает на вход блока дешифрации адреса. Далее по линии определяемой поступившим адресом посылается сигнал соответствующему регистру в блоке регистров о том, что на шине записи находятся данные, которые нужно записать. Данные записываются в регистр. Если при этом адрес записи становится равным максимальному адресу памяти, то выдается сигнал о том, что буфер полон.

Чтение из памяти осуществляется аналогичным методом. Сигнал чтения из памяти поступает в блок управления, по его приходу в блоке формирования адреса формируется адрес чтения. Сформированный адрес поступает на вход блока дешифрации адреса. Далее по линии определяемой поступившим адресом посылается сигнал соответствующему регистру в блоке регистров о том, что регистру пора выдать данные на шину чтения. Данные считываются из регистра. Если при этом адрес записи становится равным нулю, то выдается сигнал о том, что буфер пуст.

5. Функциональная схема блока управления

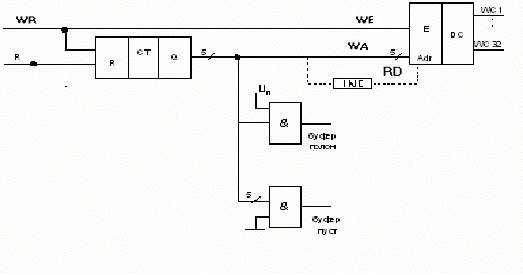

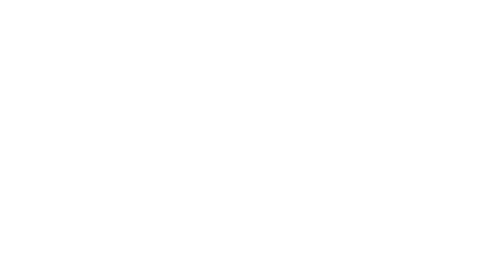

На рис. 3 представлена функциональная схема блока управления памятью

Рис. 3. Схема блока управления

Формирование адреса чтения показано пунктиром (то с использованием инкрементора).

Рассмотрим принадлежность элементов схемы структурным блокам

Блок формирования адреса состоит из реверсивного счетчика. Счетчик хранит адрес чтения и уменьшается на 1 при каждом чтении, при записи счетчик увеличивается на 1. Счетчик пятиразрядный, т.е. ведет счет от 0(00000) до 31(11111). Адрес передается по пяти адресным линиям.

Далее представлена схема реализации 5-разрядного счетчика на основе двух 4-разрядных счетчиков.

Рис. 4. Схема 5-разрядного счетчика

Для построения пятиразрядного счетчика используются два двоичных четырехразрядных счетчика К561ИЕ11 (см. п.7.1). Первый счетчик D1 считает от 0(0000) до 15(1111), при этом второй счетчик D2 переключается выходом  , но так как этот сигнал низкого уровня, то приходится ставить инвертор (К561ЛА7). При переносе разряда на второй счетчик требуется сбросить первый счетчик, для чего инверсный сигнал , но так как этот сигнал низкого уровня, то приходится ставить инвертор (К561ЛА7). При переносе разряда на второй счетчик требуется сбросить первый счетчик, для чего инверсный сигнал  посылается на вход сброса счетчика 1. Так как счетчик должен считать +1 при входе WR, то этот сигнал надо подать на вход U/D (переключатель направления счета), а при входе RD наоборот. При переполнении счетчика 2 происходит сброс обоих счетчиков. Временная диаграмма переключений приведена на рис. 5. посылается на вход сброса счетчика 1. Так как счетчик должен считать +1 при входе WR, то этот сигнал надо подать на вход U/D (переключатель направления счета), а при входе RD наоборот. При переполнении счетчика 2 происходит сброс обоих счетчиков. Временная диаграмма переключений приведена на рис. 5.

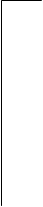

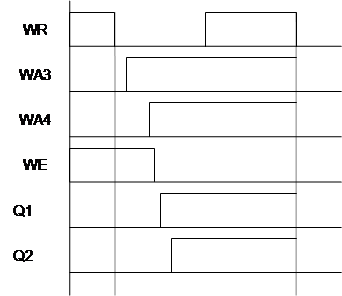

Рис. 5. временная диаграмма работы счетчиков

Блок дешифрирования адреса осуществляет доступ к регистрам в зависимости от значения адреса пришедшего по адресным линиям. Дешифратор получает значение адреса регистра от счетчика по пяти адресным линиям. В соответствии с адресом дешифратор посылает активный сигнал разрешения записи одному из регистров, который получив этот сигнал, записывает данные с шины. Аналогично действует и при чтении, получая от счетчика и инкрементора адрес считываемого регистра, он посылает активный сигнал снятия Z-состояния регистру.

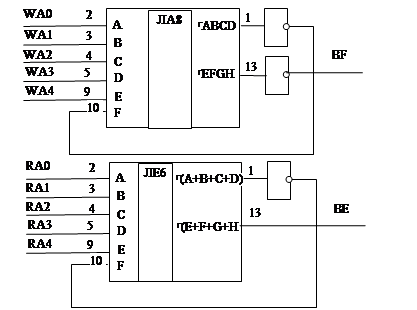

Далее представлена схема реализации дешифратора на 25

=32 адресов при помощи каскада дешифраторов К561ИД1.

Рис. 6. схема дешифратора 5 на 32

Следует заметить, что вначале приходит адрес WA0, за ним через некоторое время WA1, затем WA2, затемWA3 и последним приходит сигнал WA4, в связи с этим необходима задержка для сигнала WR/ до тех пор пока не придет последний адресный сигнал. В качестве элементов задержки используются микросхема К561ЛН1 – это логические элементы 2ИЛИ-НЕ. Данные элементы реализуют задержку сигнала чтения или записи, необходимую для корректной работы дешифратора. Так как активный уровень, разрешающий работу дешифратора, низкий то 2-ая микросхема К561ЛН1 – для инвертирования сигналов.

Временная диаграмма работы каскада дешифраторов представлена на рис. 7.

Рис. 7. Временная диаграмма переключений дешифраторов

WE/ – это сигнал WR/ после прохождения через цепочку инверторов, Q1-выход с дешифратора номера элемента (дешифратора), Q2-выход с дешифраторов адреса.

Данный блок предназначен для выявления ситуаций обнуления и переполнения памяти. Если счетчик обнулен то буфер пуст, а если наоборот все разряды счетчика единицы то «буфер полон».Смысл этих сигналов понятен из их названия.

Рис. 8. Схема проверки

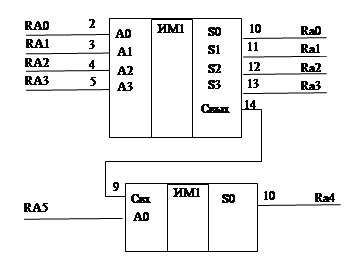

5.4 Инкрементор

Инкрементор служит для увеличения адреса при чтении на 1.

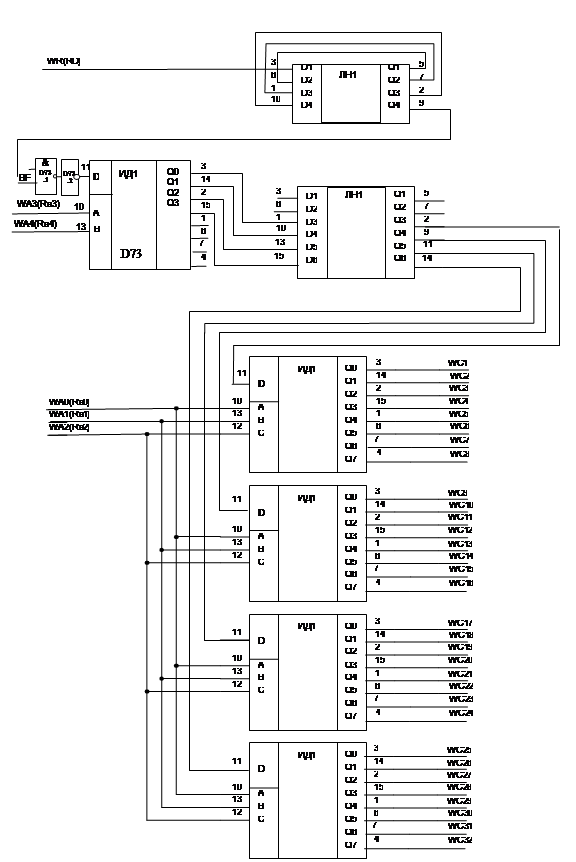

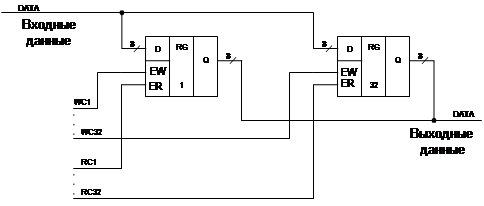

На рис. 9 представлена функциональная схема блока регистров памяти

Рис. 9. Схема блока регистров

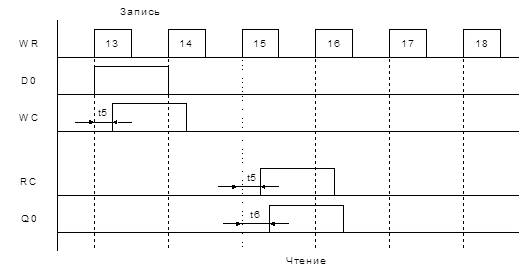

Блок регистров представляет собой набор из 32-х восьмиразрядных регистров с параллельным вводом и выводом информации. Регистры имеют Z-состояние. Входные данные поступают в блок регистров по 8-разрядной шине. С выхода блока дешифрирования адреса на регистры поступают сигналы разрешения записи и чтения. Сигнал разрешения записи WC является для регистра стробирующим, по нему регистр считывает данные с шины записи. По сигналу чтения RC регистр выходит из Z-состояния и подключается к шине чтения, данные становятся доступными для чтения.

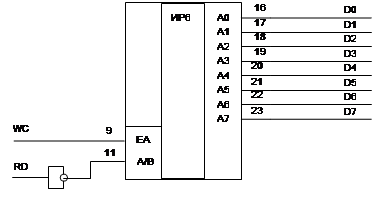

Регистр К561ИР6 имеет вид

Рис. 10. Регистр К561ИР6

Четырехразрядный двоичный реверсивный счетчик К561ИЕ11 содержит четыре триггера, срабатывающих по положительному фронту на информационных входах. Микросхема имеет следующие входы:

| Контакт

|

Обозначение

|

Описание

|

| 1

|

SE

|

Разрешение предварительной установки

|

| 2

|

Q3

|

Выход 4 разряда

|

| 3

|

S3

|

Вход 4 разряда

|

| 4

|

S0

|

Вход 1 разряда

|

| 5

|

|

Вход разряда переноса (при каскадировании)

|

| 6

|

Q0

|

Выход 1 разряда

|

| 7

|

|

Выход разряда переноса (при каскадировании)

|

| 8

|

Общ.

|

Общий

|

| 9

|

R

|

Сброс

|

| 10

|

|

Направление счета (U-больше)

|

| 11

|

Q1

|

Выход 2 разряда

|

| 12

|

S1

|

Вход 1 разряда

|

| 13

|

S2

|

Вход 2 разряда

|

| 14

|

Q2

|

Выход 3 разряда

|

| 15

|

C

|

Информационный вход

|

| 16

|

Uп

|

Питание

|

Для правильного режима работы следует на входы SE и R-подать низкий уровень, а на  , , - высокий уровень сигнала. - высокий уровень сигнала.

Универсальный дешифратор. Он применяется для преобразования входного трехразрядного кода в октальный. При этом вход В разрешает или запрещает преобразование.

Микросхема имеет следующие входы:

| Контакт

|

Обозначение

|

Описание

|

| 1

|

Q4

|

Выход

|

| 2

|

Q2

|

Выход

|

| 3

|

Q0

|

Выход

|

| 4

|

Q7

|

Выход

|

| 5

|

Q9

|

Выход

|

| 6

|

Q5

|

Выход

|

| 7

|

Q6

|

Выход

|

| 8

|

Общ.

|

Общий

|

| 9

|

Q8

|

Выход

|

| 10

|

A

|

Вход

|

| 11

|

D

|

Раз.\Запрещ.

|

| 12

|

C

|

Вход

|

| 13

|

B

|

Вход

|

| 14

|

Q1

|

Выход

|

| 15

|

Q3

|

Выход

|

| 16

|

Uп

|

Питание

|

К561ИР6 - 8-разрядный двунаправленный шинный регистр со входами и выходами как параллельными, так и последовательными.

Микросхема имеет следующие входы:

| Контакт

|

Обозначение

|

Описание

|

| 1

|

B7

|

Вход

|

| 2

|

B6

|

Вход

|

| 3

|

B5

|

Вход

|

| 4

|

B4

|

Вход

|

| 5

|

B3

|

Вход

|

| 6

|

B2

|

Вход

|

| 7

|

B1

|

Вход

|

| 8

|

B0

|

Вход

|

| 9

|

EA

|

Разреш. линии А

|

| 10

|

SI

|

Последовательный вход

|

| 11

|

A/B

|

Линия А/В

|

| 12

|

Общ.

|

Общий

|

| 13

|

P/S

|

Паралл./Послед.

|

| 14

|

A/S

|

Асин./Синх.

|

| 15

|

C

|

Тактовый

|

| 16

|

A0

|

Выход

|

| 17

|

A1

|

Выход

|

| 18

|

A2

|

Выход

|

| 19

|

A3

|

Выход

|

| 20

|

A4

|

Выход

|

| 21

|

A5

|

Выход

|

| 22

|

A6

|

Выход

|

| 23

|

A7

|

Выход

|

| 24

|

Uп

|

Питание

|

Режимы работы:

| EA

|

P/S

|

A/B

|

A/S

|

Режим

|

| L

|

H

|

H

|

L

|

Z

|

| H

|

H

|

H

|

L

|

ЗАПИСЬ

|

| L

|

H

|

H

|

L

|

Z

|

| H

|

H

|

L

|

L

|

ЧТЕНИЕ

|

| L

|

H

|

H

|

L

|

Z

|

Компаратор К561ИП2 – цифровой компаратор. Он сравнивает два четырехразрядных числа и имеет 3 выхода QA

<

B

, QA

=

B

,

QA

>

B

. Может использоваться при каскадировании.

| Контакт

|

Обозначение

|

Описание

|

| 1

|

B2

|

3 разряд слова В

|

| 2

|

A2

|

3 разряд слова А

|

| 3

|

QA

=

B

|

Выход

|

| 4

|

A>B

|

Вход

|

| 5

|

A<B

|

Вход

|

| 6

|

A=B

|

Вход

|

| 7

|

A1

|

2 разряд слова А

|

| 8

|

Общ.

|

Общий

|

| 9

|

B1

|

2 разряд слова В

|

| 10

|

A0

|

1 разряд слова А

|

| 11

|

B0

|

1 разряд слова В

|

| 12

|

QA

<

B

|

Выход

|

| 13

|

QA

>

B

|

Выход

|

| 14

|

B3

|

4 разряд слова В

|

| 15

|

A3

|

4 разряд слова А

|

| 16

|

Uп

|

Питание

|

| Тип

|

Потребляемый ток, мкА

|

Время задержки,нс

|

| ИЕ11

|

20

|

150

|

| ИР6

|

20

|

300

|

| ЛН1

|

0,02

|

190

|

| ИД1

|

5

|

167

|

| ЛА7

|

0,25

|

60

|

| ЛА8

|

1

|

85

|

| ЛЕ6

|

0,25

|

70

|

| ИМ1

|

20

|

600

|

| ЛЕ5

|

1

|

60

|

| Обозначение

|

Наименование

|

Количество

|

| D1

|

ЛЕ5 – 4 эл.2ИЛИ-НЕ

|

1

|

| D3,D5

|

ИЕ11-СЧЕТЧИК

|

2

|

| D2,D4,D9-D71(НЕЧЕТНЫЕ),D73.2 D80,D81,D82

|

Элемент НЕ

|

38

|

| D6,D7

|

ИМ1-СУММАТОР

|

2

|

| D8-D70 (ЧЕТНЫЕ)

|

ИР6-РЕГИСТР

|

32

|

| D72,D74

|

ЛН1-6ИНВЕРТОРОВ

|

2 по 4 эл.

|

| D73,D75,D76,D77,D78

|

ИД1-ДЕШИФРАТОР

|

5

|

| D73.1

|

ЛА7-4 ЭЛЕМЕНТА 2И-НЕ

|

1

|

| D79

|

ЛА8 – 2 ЭЛ. 4И-НЕ

|

1

|

| D83

|

ЛЕ6 – 2ЭЛ.4ИЛИ-НЕ

|

1

|

Можно заменить отдельные элементы НЕ микросхемой ЛН1- тогда этих схем нужно будет 8(DN1-DN8).

Напряжение питания +5В подать:

на 16-й вывод микросхем D3, D5, DN1-DN8, D6,D7, D73,D75,D76,D77,D78

на 14-й вывод микросхемы D1, D73.1, D79, D83

на 24-й вывод микросхем регистров.

на 13-й вывод микросхем регистров,

на 6-й вывод микросхем D6

К цепи ОБЩ. подключить:

1-й вывод микросхем D3, D5,D7,регистров, D73

2-й вывод микросхем D6,D7,регистров

3-й вывод микросхем D3, D5,D7,регистров

4-й вывод микросхем D1, D3, D5, DN1-DN8, D6,D7,регистров, D73, D73.1

5-й вывод микросхем D1, D3, D5,D7,регистров, D73,D75,D76,D77,D78, D73.1

6-й вывод микросхем D1,D7,регистров, D73, D73.1, D79, D83

7-й вывод микросхем D1, D5,регистров, D73, D73.1, D79, D83

8-й вывод микросхем D1, D3, D5, DN1-DN8, D6,D7,регистров, D73,D75,D76,D77,D78 , D73.1, D79, D83

9-й вывод микросхем D1, D6, D73,D75,D76,D77,D78, D73.1

10-й вывод микросхем D1,регистров, D73.1

11-й вывод микросхем D1, DN8,D7, D73.1, D79, D83

12-й вывод микросхем D1, D3, D5, DN1-DN8,D7,регистров, D73, D73.1, D79, D83

13-й вывод микросхем D1, D3, D5, DN8,D7, D73.1

14-й вывод микросхем D5, DN8,D7,регистров

15-й вывод микросхем DN8, D6,D7,регистров

9. Временные диаграммы

ta0

– время задержки 1-й адресной линии

ta1

– время задержки 2-й адресной линии

ta2

– время задержки 3-й адресной линии

ta3

– время задержки 4-й адресной линии

ta4

– время задержки 5-й адресной линии

ta0

= 60+190+150=400 нс

ta1

= ta0

+150нс = 550нс

ta2

= ta0

+150нс = 700нс

ta3

= ta0

+150 = 850нс

ta4

= ta0

+tне

+ta3

= 150нс+190нс+850 = 1190нс

Время формирования адреса чтения или записи: 1190 нс.

9.2. Временная диаграмма блока дешифрирования адреса

t3

– Задержка на элементах D73, D73.1, D73.2

t4

– Задержка на элементе D74

t5

– Задержка дешифрирования

t3

= 190+60+167=417нс

t4

= 190 нс

t5

= 167нс

t=t3+t4+t5=764 нc

Время дешифрации адреса чтения или записи: 724 нс.

9.3 Временная диаграмма блока проверки заполнения памяти

t7-задержка на ЛА8

t8

–t7+ задержка на НЕ

t9

– t8+задержка на ЛА8

t10 – t9+задержка на НЕ

t7

=85 нс

t8

= 175нс

t9

= 260нс

t10=450 нс

Максимальное время обнаружения переполнения(пустоты): 450 нс

9.4 Временная диаграмма блока регистров

t6

– время переключения регистра из Z-состояния

t6

= 300нс

Тогда максимальная частота работы памяти: f

раб.

= 1/tи

= 3 Мгц.

В спроектированном устройстве регистровой памяти используется серия КМОП К561. Напряжение питания данной серии Uпит.

=+5В±10%. Входные и выходные логические уровни сигналов совместимы внутри одной серии, в данном случае 561.

Все элементы данного устройства принадлежат одной серии 561, это значит, что емкостные параметры входов и выходов согласованны.

Расчет потребляемой мощности производится в следующем порядке. Сначала в справочных данных находятся значения потребляемых токов Iпотр.

для каждой микросхемы. Далее рассчитывается потребляемая мощность одной микросхемы данного типа. Затем полученное значение помножается на число таких микросхем в устройстве. Полученные значения складываются между собой, образуя суммарную потребляемую мощность.

Pпотр.

= Iпотр.

Uпит.

Таблица результатов расчета

| Тип

|

Потребляемый ток, мкА

|

Кол-во

|

Мощность

|

| ИЕ11

|

20

|

2

|

40

|

| ИР6

|

20

|

32

|

640

|

| ЛН1

|

0,02

|

8

|

0,16

|

| ИД1

|

5

|

5

|

25

|

| ЛА7

|

0,25

|

1

|

0,25

|

| ЛА8

|

1

|

1

|

1

|

| ЛЕ6

|

0,25

|

1

|

0,25

|

| ИМ1

|

20

|

2

|

40

|

| ЛЕ5

|

1

|

1

|

1

|

Итого общая мощность схемы получилась = 747,66 мкВт.

В результате работы изучены основные принципы работы буферных элементов, в частности буферов типа "очередь". Разработанная структурная схема полностью раскрывает внутреннюю структуру данного типа памяти. Полученные функциональные схемы блока управления и блока регистров выявляют детали функционирования соответствующих частей устройства. На этапе проектирования принципиальной схемы получены дополнительные знания по составу серии К561 и номенклатуре ее элементов. Изучены базовые принципы расчета параметров устройства и временного согласования сигналов. Построенные диаграммы выявили, что спроектированное устройство может корректно функционировать на частотах вплоть до 3 МГц.

1. Шило В.Л. Популярные цифровые микросхемы: Справочник.-2-е изд.-М.: Радио и связь,1989.- 352с.

2. Потемкин И.С. Функциональные узлы цифровой автоматики.-М.: Энергоатомиздат,1988.-320с.

3. Петровский И.И. Логические ИС КР1533, КР1554. Справочник. -М.: Бином,1993.-496с.

4. Применение интегральных схем: Практическое руководство. В 2-х кн. Пер. с англ./ Под ред. А. Уильямса.-М.: Мир,1987.-432с.

5. Пухальский Г.И. Проектирование дискретных устройств на интегральных микросхемах: Справочник. –М.: Радио и связь,1990.-304с.

6. Угрюмов Е.П. Цифровая схемотехника. -СПб.: БХВ-Петербург,2001.-528с.

|