Структурная схема микропроцессора.

Введение.

Характерной чертой научно-технического прогресса, определяющей мощный дальнейший подъем общественного производства, является широкое внедрение электроники во все отрасли народного хозяйства.

Современная электронная цифровая вычислительная техника широко применяется в народном хозяйстве. В настоящее время создано четыре поколения ЭВМ с улучшающимися технико-экономическими показателями, что способствует дальнейшему расширению сферы применения ЭВМ и их эффективности.

Четвертое поколение ЭВМ на основе интегральных схем с большой степенью интеграции элементов (БИС) появилась в начале 70 - х годов и существенно изменило параметры ЭВМ всех классов. Вместе с тем возник совершенно новый класс ВТ на основе БИС - микропроцессорные вычислительные машины - микроЭВМ.

В конце 70 - х годов в результате интеграции всех электронных устройств ЭВМ в одном кристалле были созданы однокристальные микроЭВМ, вычислительная мощность которых не уступает вычислительной мощности средних ЭВМ начала 70 - х годов.

Микропроцессоры и микроЭВМ стали новым массовым классом ЭВМ вследствие малой материалоемкости и стоимости , низкого энергопотребления и высокой надежности . Отечественной промышленностью ежегодно производится несколько десятков тысяч микроЭВМ, .), сотни тысяч микропроцессоров и микрокалькуляторов на их основе. Разрабатываются операционные системы общего применения и стандартное программное обеспечение микроЭВМ.

Массовость этого нового класса и его высокие технико-экономические параметры оказывают революционизирующее влияние на целое поколение приборов, оборудования, агрегатов со встроенными микропроцессорными средствами.

Микропроцессоры и микроЭВМ применяют в различных областях народного хозяйства (в управлении технологическими процессорами , информационных и измерительных комплексах, энергетике , медицине и др. ). На базе выпускаемых микропроцессоров и микроЭВМ созданы высокопроизводительные устройства числового программного управления . Крупносерийное производство ряда моделей мини - ЭВМ позволяет начать работы по созданию нескольких типов проблемно - ориентированных комплексов для автоматизации научных исследований и технологических процессов. Особое значение микроЭВМ приобретают в связи с реализацией школьной реформы. МикроЭВМ положены в основу организуемых в каждой школе учебных классов по дисциплине “ Основы информатики и вычислительной техники”.

Построение ЭВМ на основе микропроцессорных БИС позволяет уменьшить стоимость микроЭВМ, сравнимых по своим параметрам с ранее созданными ЭВМ , в 103 - 104 раз , габаритным размерам - в ( 2 - 3 ).104 раз , по мощности потребления - в 105 раз. Это означает , что без увеличения общих затрат микроэлектронная технология позволяет обществу произвести в сотни и тысячи раз больше ЭВМ , чем ранее.

Микропроцессор

– функционально законченное устройство обработки информации, управляемое хранимой в памяти программой. Появление микропроцессоров (МП) стало возможным благодаря развитию интегральной электронике. Это позволило перейти от схем малой и средней степени интеграции к большим и сверхбольшим интегральным микросхемам (БИС и СБИС).

По логическим функциям и структуре

МП напоминает упрощенный вариант процессора обычных ЭВМ. Конструктивно он представляет собой одну или несколько БИС или СБИС.

По конструктивному признаку МП можно разделить на однокристальные МП с фиксированной длиной (разрядностью) слова и определенной системой команд; многокристальные (секционные) МП с наращиваемой разрядностью слова и микропрограммным управлением (они состоят из двух БИС и более).

В последнее время появились однокристальные МП с микропрограммным управлением.

Архитектура многокристального МП с микропрограммным управлением позволяет достичь гибкости в его применении и сравнительно простыми средствами организовать параллельное выполнение отдельных машинных операций, что повышает производительность ЭВМ на таких МП.

Несмотря на то, что возможности многокристальных МП существенно выше, чем у однокристальных, многие прикладные задачи успешно решаются на основе однокристального микропроцессора.

Описание структурной схемы микропроцессора.

В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров.

Арифметическо-логическое устройство

состоит из двоичного сумматора со схемами ускоренного переноса, сдвигающего регистры и регистров для временного хранения операндов. Обычно это устройство выполняет по командам несколько простейших операций: сложение, вычитание, сдвиг, пересылку, логическое сложение (ИЛИ), логическое умножение (И), сложение по модулю 2.

Устройство управления

управляет работой АЛУ и внутренних регистров в процессе выполнения команды. Согласно коду операций, содержащемуся в команде, оно формирует внутренние сигналы управления блоками МП. Адресная часть команды совместно с сигналами управления используется для считывания данных из определенной ячейке памяти или для записи данных в ячейку. По сигналам УУ осуществляется выборка каждой новой, очередной команды.

Блок внутренних регистров

БВР, расширяющий возможности АЛУ, служит внутренней памятью МП и используется для временного хранения данных и команд. Он также выполняет некоторые процедуры обработки информации.

На рисунке (2) приведена более подробная структурная схема однокристального МП. Здесь блок внутренних регистров содержит регистры общего назначения и специальные регистры: регистр-аккумулятор, буферный регистр адреса, буферный регистр данных, счетчик команд, стека, признаков.

Регистры общего назначения

(РОН), число которых может изменятся от 4 до 64, определяют вычислительные возможности МП. Их функция – хранение операндов. Но могут выполнять также и роль регистров. Все РОН доступны программисту, который рассматривает их как сверхоперативное запоминающее устройство.

Регистр – аккумулятор

(“накопитель”), предназначен для временного хранения операнда или промежуточного результата действий производимой в АЛУ. Разрядность регистра равна разрядности информационного слова.

Буферный регистр адреса

служит для приема и хранения адресной части выполняемой команды. Возможное количество адресов, определяется разрядностью регистра.

Буферный регистр данных

используется для временного хранения выбранного из памяти слова перед передачей его во внешнюю шину данных. Его разрядность определяется количеством байт информационного слова.

Счетчик команд

содержит адрес ячейки памяти, в которой помещены байты выполняемой команды.

Регистр команд

принимает и хранит код очередной команды, адрес которой находится в счетчике команд. По сигналу УУ в него передается из регистра хранимая там информация.

Регистры стека

делятся на стек и указатель стека. В МП стек – набор регистров, хранящих адреса команд возврата при обращении к подпрограммам или состояние внутренних регистров при обработке прерываний. Стек может быть выполнен не только на внутренних регистрах МП, составляя его часть, но и находиться в ОЗУ, занимая там отведенную для него зону. В последнем случае для обращения к нему необходим специальный регистр – указатель стека.

Указатель стека

хранит адреса последней занятой ячейки стека, которую называют вершиной. Содержащее в указателе число указывает, где находится вершина стека. Когда в стек записывается очередное слово, то число в указателе стека соответственно увеличивается. Извлечение слова из стека сопровождается, наоборот, уменьшением числа, заполняющего указатель стека. Кроме такой процедуры предусматривается возможность считывания без разрушений содержимого любой ячейки стека при неизменном числе, хранимом в указателе стека.

Регистр признаков

представляет собой набор триггеров – флажков. В зависимости от результатов операций, выполняемых АЛУ, каждый триггер устанавливается в состояние 0 или 1. Флажковые биты, определяющие содержимое регистра, индицируют условные признаки: нулевого результата, знака результата, перевыполнения и т. п. Эта информация, характеризующая состояние процессора, важна для выбора дальнейшего пути вычислений.

Рассмотрим более подробно основные части микропроцессора (рис. 2).

Внутренняя шина данных

соединяет собой основные части МП.

Шиной

называют группу линий передачи информации, объединенных общим функциональным признаком. В микропроцессорной схеме используется три вида шин: данных, адресов и управления.

Разрядность внутренней шины данных т. е. количество передаваемых по ней одновременно (параллельно) битов числа соответствует разрядности слов, которыми оперирует МП. Очевидно, что разрядность внутренней и внешней шин данных должна быть одной и той же. У восьмиразрядного МП внутренняя шина данных состоит из восьми линий, по которым можно передавать последовательно восьмиразрядные слова – байты. Следует иметь в виду, что по шине данных передаются на только обрабатываемые АЛУ слова, но и командная информация. Следовательно, недостаточно высокая разрядность шины данных может ограничить состав (сложность) команд и их число. Поэтому разрядность шины данных относят к важным характеристикам микропроцессора – она в большей мере определяет его структуру (числа разрядов указаны на рисунке в скобках рядом с названиями блоков).

Шина данных МП работает в режиме двунаправленной передачи, т. е. по ней можно передавать слова в обоих направлениях, но не одновременно. В этом случае требуется применение специальных буферных схем и мультиплексного режима обмена данных между МП и внешней памятью. Мультиплексный режим

(от английского слова multiple – многократный, множественный), иногда называемый многоточечным

, - режим одновременного использования канала передачи большим числом абонентов с разделением во времени средств управления обменом.

Мультиплексор

– устройство, которое выбирает данные от одного, двух (или более) входных информационных каналов и подает эти данные на свой выход. Схема мультиплексора состоит из двухвходовых логических элементов И – ИЛИ, управляемых распределителем импульсов. Промышленностью выпускаются мультиплексоры, которые могут входить в состав , а также в виде отдельных БИС (например, восьмивходовый одноразрядный; двухвходовый четырехразрядный; трехвходовый четырехразрядный и др.).

Демультиплексор

– устройство, выполняющее противоположную мультиплексору функцию, - подает данные, подводимые к его входу, на один (или более) выходной информационный канал.

Мультиплексоры и демультиплексоры позволяют компоновать из микропроцессорных элементов микроЭВМ для любой длины машинного слова. Предположим, что задача обработки данных заключается в сложении двух операндов, каждый из которых представляет собой восьмиразрядное двоичное число – байт.

Восьмиразрядное арифметически – логическое устройство

выполняет все арифметические и логические операции. На первый вход АЛУ поступает байт из восьмиразрядного аккумулятора

, а на второй вход – из восьмиразрядного промежуточного регистра

. Результат сложения указанных двух байтов передается с выхода АЛУ через внутреннюю шину данных в аккумулятор. Такая организация удовлетворяет одноадресной организации микропроцессора. Для нее характерно то, что один из операндов, участвующих в обработке, всегда находится в аккумуляторе, адрес которого задан неявно. Поэтому при выполнении операции сложения двух операндов требуется указывать только один адрес – второго операнда, содержащегося, например в одном из восьми регистров общего назначения

(РОН). К АЛУ подключены регистр признаков

, предназначенный для хранения и анализа признаков результата операции, и схема десятичной коррекции

(на рис. 2 не показана), позволяющая проводить обработку данных в двоично-десятичном коде.

В состав микропроцессора входят также указатель стек, счетчик команд, буферный регистр адреса, ОЗУ. Первые два РОН – регистры W и Z – предназначены для кратковременного хранения данных во время выполнения команды (эти регистры недоступны программисту), остальные шесть РОН – регистры B, C, D, E, H и L – cлужат ячейками внутренней памяти, называемой сверхоперативным запоминающим устройством

(СОЗУ). В них хранятся операнды, подлежащие обработки в АЛУ, результаты обработки данных, выполненных в АЛУ, и управляющие слова. В каждом регистре помещается один байт. Обращение к РОН – адресное. Попарное расположение регистров B и C, D и E, H и L дает возможность проводить обработку двухбайтовых слов, называемую обработкой “удвоенной точности”. Обмен данными с РОН (считывание и запись информации) осуществляется через мультиплексор

, причем требуемый регистр выбирается с помощью селектора регистров по сигналу УУ

.

В левой части рис. 2 расположены регистр команд, дешифратор кода операции и УУ (хотя дешифратор относится к УУ, он нарисован отдельно для большей наглядности). Стековый регистр адреса на рисунке отсутствует, так как стек представляет собой определенную зону ОЗУ.

Обмен информацией между регистрами и другими блоками микропроцессора производится через внутреннюю шину данных, причем передачи команд и данных разделены во времени. Связь с внешней шиной данных осуществляется через буферный регистр данных

.

Микропроцессор – это программно-управляемое устройство. Процедура выполняемой им обработки данных определяется программой, т. е. совокупностью команд. Команда делится на две части: код операции и адрес. В коде операции заключена информация о том, какая операция должна быть выполнена над данными, подлежащими обработке. Адрес указывает место, где расположены эти данные (в регистрах общего назначения микропроцессора, т. е. во внутренней или внешней памяти). Слово данных, подвергаемое обработке, представляет один байт. Команда может состоять из одного, двух или трех байтов, последовательно расположенных в памяти.

Первый байт команды содержит код операции. Считанный в начале интервала выполнения команды, называемого циклом команды, ее первый байт поступает по внутренней шине данных в регистр команд, где хранится в течение всего цикла. Дешифратор кода операции дешифрует содержимое регистра команд – определяет характер операции и адреса операндов. Эта информация подается в УУ, которое вырабатывает управляющие сигналы, направляемые в блоки микропроцессора, участвующие в выполнении данной команды.

В том случае, когда код операции непосредственно указывает адрес данных – объекта обработки, операция начинается сразу после считывания первого байта команды. Если же в команде содержится более одного байта, то остальные байты, несущие информацию об адресе ячейки памяти, где хранятся данные, передаются либо в буферный регистр адреса, либо в один из РОН только после завершения всей процедуры считывания команды или, иначе говоря, после получения полной информации о местонахождении операндов и о том, какая операция должна выполнятся, начинается операция.

Рассмотрим пример выполнения операции сложения двух операндов. Первый операнд хранится в аккумуляторе, второй в одном из РОН (его адрес указан в команде), откуда он передается в промежуточный регистр. Согласно коду операции АЛУ суммирует поступающие на его вход байты и выдает результат, который фиксируется в аккумуляторе. Этот результат можно использовать при дальнейших этапах обработки.

Наряду с многокристальными и однокристальными МП используются секционированные или разрядно-модульные МП. Основной их отличительной особенностью является то, что каждый модуль предназначен для обработки нескольких разрядов машинного слова, а слово в целом обрабатывается группой модулей или секций, соединенных между собой.

Основные микропроцессорные комплекты и их функциональный состав.

Наибольшее распространение получили микропроцессоры, управляемые по программам или микропрограммам. Такие МП строятся на базе ЭСЛ, ТТЛШ, КМОП, И2

Л и других распространенных элементов. Современные микропроцессоры представляют собой набор БИС, соединенных между собой определенным образом, которые составляют так называемые микропроцессорные комплекты (МПК).

Микропроцессорные комплекты изготовляют в виде секционных БИС с возможностью наращивания. Исключение составляет БИС КР580ИК80А – восьмиразрядный МП, в котором можно увеличить разрядность обрабатываемых данных путем двойного пересчета. В состав секционных МПК входят как правило, п

-разрядная МП секция, предназначенная для обработки информации и временного хранения результатов, схема микропрограммного УУ, а также БИС, выполняющие функции по обработке прерываний программы, синхронизации и связи с периферийными устройствами.

Возможность наращивания разрядности обрабатываемой информации и применение микропрограмм обеспечивают гибкость и широкую сферу применения секционных МПК, так как разработчик аппаратуры сам может определять набор команд.

В структуре МПК можно выделить операционную и управляющую части. Операционная часть поводит логическую обработку информации, управляющая часть декодирует команды и формирует сигналы, необходимые для выполнения той или иной операции. Каждая команда представляет собой небольшую программу, состоящую из элементарных операций. Последовательность таких команд называется микропрограммой. Очередность команд, в соответствии с которой работает управляющая часть МП, называется программой.

Первые МП строились на р

-канальных МОП-транзисторах, поэтому имели невысокое быстродействие. В дальнейшем появились МП, в которых использовались п

-канальные МОП-транзисторы и биполярные интегральные структуры (И2

Л, ТТЛШ и ЭСЛ), что привело к значительному увеличению быстродействия.

Количество различных операций, выполняемых некоторыми МП, доходит до 100, причем в них предусматриваются операции с двойной длиной слова и побайтовой обработкой информации. В процессе развития наряду с МП, имеющими фиксированный список команд, появились МП с микропрограммным управлением, которое позволяет изменять список команд и алгоритмы управления. Это увеличивает гибкость процессора и упрощает реализацию последовательности относительно сложных микрокоманд.

Важнейший параметр МП - быстродействие. В настоящее время диапазон быстродействия МП - от десятков тысяч до 1- 3 млн. коротких операций.

Отечественная промышленность выпускает секционированные микропроцессорные комплекты серий К-589, КР-1802, КР-1804, К18-00 и др.

Секционированый микропрцессорный комплект БИС серии К589.

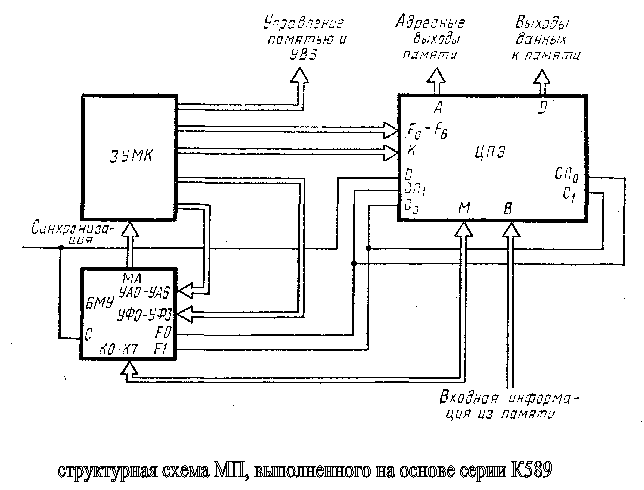

Микропроцессрный комплект БИС серии к 589 состоит из восьми микросхем, выполненных по ТТЛШ-технологии , блоков микропрограмного управления (БМУ) К 589ИК01; центрального процессорного элемента (ЦПЭ) К589ИК02; схем ускореного переноса (СУП) К89ИК03 и мног режимног буферного регистра (МБР) К589ИР12; блока приоритетных прерываний (БПП) К589ИК14; шинных формирователей без инверсий (ШФ) К589АП16 и с инверсией (ШФИ) К589АП16; схемы синхронизации и управления (МСУ) К589ХЛ4.

Комплект обеспечивает построение автонмных микро- и мини- ЭВМ, контроллеров, устройств автоматики с различной архитектурой благодаря модульности структуры, возможности паралельного наращивания микропрограмнго управления, совместимости с ТТЛ-транзисторами серии к155 и др.

Микросхемы герметезированы в пластмассовых корпусах с вертикальным расположением выводов.

Соединяя параллельно несколько МП, можно получить процессор с требуемой длиной слова. Для реализации 16-разрядного процессора, содержащего УУ, шины и микропрограммное ЗУ, требуется примерно 20 БИС и 10 ИС. Такой процессор заменяет эквивалентную систему на ТТЛ ИС среднего уровня интеграции, имеющую более 200 корпусов. Центральный микропроцессор (ЦП) в нем состоит из восьми микросхем ЦПЭ, оног БМУ, ЗУМК.

На рис 3 показана структурная схема такого процессора. Микропрограмма, находящаяся в управляющей памяти, после выключения питания устанавливает ЦП в исходное состояние и осуществляет выборку и выполнение команд. Разрядность слова микропрограммной памяти определяется числом и разрядностью микроинструкций.

Центральный процессорный элемент имеет шесть групп входов и выходов, по которым происходит связь с другими схемами. Четыре из них (В, М, А, D) используются преимущественно для связи с внешней памятью и устройствами ввода – вывода. Группа выводов F0

– F6

используется для управления работой ЦПЭ, а входы К – для маскирования информации для занесения константы.

Блок микропрограммного управления. Он имеет восемь входов команды К (макрокоманды). Таким образом, информация о коде операции определяется восемью разрядами, т. е. максимальное число макрокоманд 256. Число разрядов микрокоманды, требуемое для управления БМУ, равно: семь разрядов УАО – УА6 – для управления выработкой перехода к следующему адресу микрокоманды и четыре УФ0 – УФ3 – для управления схемой выработки признаков условных переходов. Таким образом, для управления ЦПЭ и БМУ необходимо 19 разрядов. Кроме этих микроинструкций необходимы дополнительные микроинструкции для управления памятью, вводом – выводом и т. д.

Данные в АЛУ поступают из памяти из устройства ввода информации и одаются в регистр-аккумулятор. В него поступают также результаты операций, выполняемых в АЛУ. После завершения операций данные посылаются в память или в устройства вывода информации.

Устройство управления управляет операциями в соответствии с содержанием команд, которые считываются из внешнего ЗУ, и помещаются в регистр команд. Адрес очередной команды обычно определяется счетчиком команд. В качестве регистра и счетчика команд используются внутренние регистры ЦПЭ.

Связь с ЗУ осуществляется через регистр адреса памяти и регистр данных памяти, выходы которых соединены с соответствующими адресными и информационными сигналами. Разрядность адреса памяти определяет адресуемое поле памяти. Часть регистров МП используется в качестве сверхоперативной памяти, в которой хранятся промежуточные результаты вычислений. Это позволяет повысить быстродействие процессора.

Для обеспечения контроля за состоянием регистров при выполнении операций используются регистры состояний блока микропрограммного управления (БМУ). Триггеры этих регистров (флажки) индицируют переполнение регистров ЦПЭ, нулевое содержание аккумуляторов, знак его содержимого и другие состояния. Эта информация используется для организации условных переходов в микропрограммах.

Синхронизация работы отдельных узлов процессора осуществляется одной или несколькими сериями тактовых импульсов. Для реализации одной команды необходимо несколько периодов тактовых импульсов. Командный цикл состоит из цикла выборки, во время которого вырабатывается адрес команды и по нему вырабатывается команда и считываются в регистр данные из памяти, и цикла , исполнительного, во время которого в устройстве управления команда дешифруется и процессор исполняет ее.

Рассмотрим подробно структуру и основные характеристики отдельных БИС комплекта серии К589.

Центральный процессорный элемент предназначен для логической и арифметической обработки информации, приема, хранения и выдачи оперативной информации, а также для формирования адресов памяти. Он представляет собой двухразрядную микропроцессорную секцию со структурой, обеспечивающей практически неограниченные возможности объединения кристаллов ЦПЭ по горизонтали с целью увеличения разрядности процессора.

Основная особенность ЦПЭ – большое число шин: три входные и две выходные с адресным регистром данных это обеспечивает возможность выдачи данных и адресов в память одновременно. Назначение шин ЦПЭ – пересылка байтов, тестирование битов, ввод – вывод информации во внутренние регистры.

Формирователи выходных шин выполнены на элементах с тремя состояниями, что существенно упрощает подключение УПЭ к магистрали. Шина микрофункций управляет работой секций, выбирая операнды и операции, которые должны выполнятся в АЛУ. ЦПЭ выполняет свыше 40 логических и арифметических операций. Секция выдает сигналы ускоренного переносы. Кроме того, она снабжена независимыми линиями входа и выхода переноса, входа и выхода сдвигаемого кода.

В состав ЦПЭ входят АЛУ, 11 сверхоперативных регистров, два мультиплексора (А и В), аккумулятор, регистр адреса памяти, дешифратор микрофункций.

Информация на ЦПЭ поступает по трем группам независимых входов М, В и К из основной памяти, устройств ввода – вывода, памяти микропрограмм. Информация, поступающая на ЦПЭ, хранится в 11 регистрах R0

– R9

, T , а также в накапливающем регистре АС или в регистре адреса памяти. Через мультиплексоры А и В информация передается в АЛУ. Регистры R0

- R9

и Т выполняют функции сверхоперативного запоминающего устройства и могут быть использованы как счетчики. Информация с регистров через мультиплексор А поступает в АЛУ, а с выхода АЛУ – снова на регистры. Аккумулятор служит для хранения результата операций АЛУ. Информация с выхода аккумулятора поступает на вход АЛУ или через выходной усилитель – буфер – может выдаваться на выходную магистраль для передачи в основную память или на устройство ввода – вывода. Через мультиплексоры А и В она может подаваться на один из двух входов АЛУ. На входы мультиплексора А поступают данные со входов М, регистров R0

– R9

, Т и аккумулятора, а на входы мультиплексора В – информация со входов В , К и аккумулятора. При этом производится маскирование информации входов В и АС данными на входах К. результат операций, выполняемых в АЛУ, может хранится в R0

– R9

и аккумуляторе.

При операции сдвига в право используют вход СП1 и выход СП0, для организации последовательного переноса - вход С1 и выход С0. Наличие выходов Х и У обеспечивает организацию ускоренного (сквозного) переноса между микросхемами ЦПЭ. При неарифметических операциях схемы переноса используют для выполнения логического ИЛИ всех разрядов слова с учетом маскирования по входам К. Входом К пользуются при арифметических операциях для маскирования полей и отдельных разрядов обрабатываемых слов. Через входы К в ЦПЭ могу подаваться константы из памяти микропрограмм. Обычно регистр адреса используется для хранения и пересылки адреса команд в основную память. В этом случае информация с АЛУ через отдельный выход поступает на регистр памяти. В каждом микрокомандном цикле на входы F поступает микроинструкция (часть поля микрокоманды,), которая дешифруется и определяет выполнение необходимы операций ЦПЭ. Микроинструкция F0-F6 разбита на два поля F и R- группы. F -группы (F4-F0) определяет код операции, регистровая R- группа (F0-F3) - адрес регистров.

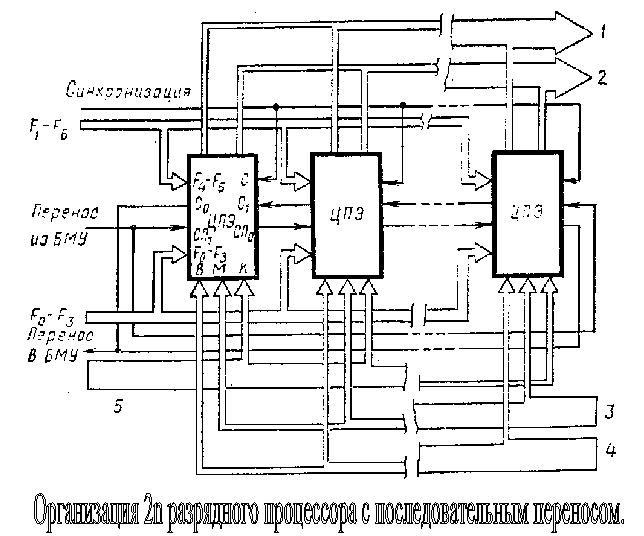

На рис. 4 показан вариант соединения БИС ЦПЭ с последовательным переносом, осуществляемым с помощью БИС ускоренного переноса. Цикл обработки ЦПЭ составляет 100 нс.

Блок микропрограммного управления предназначен для управления последовательностью выборки микрокоманд из управляющей памяти (ЗУМК) и выполняет следующие функции: управление регистром адреса микрокоманды; выборку очередной микрокоманды с учетом содержимого РАМК; хранение и выдачу признаков; управление микропрограммными прерываниями. В состав БМУ (рис. 5) входят: девятиразрядный регистр адреса микрокоманд и соответствующая магистраль; схема формирования очередного адреса; выходные буферы адреса микрокоманды на элементах с тремя состояниями; триггеры признаков (C, Z, Ф); регистр команды; выходной буфер флажков.

Формирование адреса очередной микрокоманды выполняется с помощью условных и безусловных переходов. В каждой текущей микрокоманде содержится поле микроинструкции БМУ, предназначенной для формирования адреса следующей микрокоманды. Адреса микрокоманды (всего 512) образуют матрицу (страницу), состоящую из 32 строк и 16 столбцов. Каждый адрес определяется номером той строки и того столбца, на пересечении которых он находится. Под адрес строки отводится пять разрядов (МА8

– МА4

), а под адрес столбца четыре разряда (МА3

– МА0

). Девятиразрядный адрес микрокоманды, выработанный логикой следующего адреса, загружается в регистр адреса микрокоманд, а из него выдается в память микрокоманд по десяти выходным шинам.

Блок микропрограммного управления обеспечивает хранение текущего значения на выходе переноса ЦПЭ (С0, СП0) и управляет информацией на входе переноса (С1, СП1). С помощью двух групп микроинструкций осуществляется управление признаками - установка и их выдача. Схема обработки признаков содержит три триггера: С и Z и триггер - защелку Ф, в которой запоминается текущее состояние выхода переноса ЦПЭ. Логическая схема признаков совместно со схемой переноса ЦПЭ используется для выполнения арифметических и сдвиговых операций.

Сигнал в двоичном коде на входах УА используется для формирования адресов строки и столбца и вида микроопераций, выполняемой БМУ. По четырем микроинструкциям производятся безусловные переходы, по остальным - условные. Для формирования адреса следующей микрокоманды при безусловных переходах используется адрес текущей микрокоманды, который хранится в регистре адреса и ряд битов микроинструкции УА0

-УА6

: при условных переходах - адрес текущей (предыдущей) микрокоманды и содержимое регистров С, Z или Ф либо код старших разрядов К4

-К7

. Для выработки следующего адреса микрокоманды по содержимому данных на шинах К4

-К7

используется часть адреса текущей микрокоманды и несколько разрядов кода на шинах УА.

Управление схемой обработки признаков (C, Z и Ф) осуществляется с помощью микроинструкции на входах УФ0

– УФ3

. Информация на входе Ф записывается в триггер Ф и затем в триггер С или Z. По входу ЗМ дается разрешение на запись информации со входов К в регистр адреса микрокоманд. Разрешение на прерывание выдается с выходной шины СРП при микроинструкции ПЕРЕХОД В НУЛЕВУЮ СТРОКУ, что означает конец выполнения микропрограммы (команды). Обычно сигнал с шины СРП подается на входную шину СРП блока приоритетного прерывания. Этот блок может ответить на прерывание выдачей сигнала подтверждения прерывания, что блокирует выдачу следующего выбранного адреса строки из БМУ. Тогда при выдаче нового адреса микрокоманды на линию адреса строки можно подавать адрес извне минуя БМУ, что позволяет перевести микропрограмму на программу обработки прерывания. Измененный адрес строки, переданный на адресные линии микрокоманд, не изменяет содержимого регистра адреса микрокоманд. Таким образом, последующая функция перехода будет использовать адрес строки в регистре адреса микрокоманды, а не измененный адрес строки.

Цикл БМУ составляет 85 нс. Имеется возможность адресации 512 микрокоманд (предусмотрена возможность наращивания числа адресуемых микрокоманд). Корпус микросхемы типа ДИП с 40 выводами.

Схема ускоренного переноса (СУП)

предназначена для формирования групповых переносов при совместном использовании с ЦПЭ в многоразрядных сумматорах. Микросхема позволяет объединить до восьми ЦПЭ, т. е. образовать 16-разрядный сумматор.

Схема имеет 17 информационных входов, 8 информационных выходов и один управляющий вход, позволяющий управлять выходом самого старшего переноса.

В каждом ЦПЭ формируются сигналы подготовки сквозного переноса, которые подаются в схему ускоренного переноса, а она в свою очередь вырабатывает сигналы переносов, поступающие в ЦПЭ. Если в каждом разряде 1, то сигнал подготовки также 1 и через данную секцию происходит перенос от младшей к старшей. Так как схема ускоренного переноса генерирует сигналы переносов во все ЦПЭ одновременно вне зависимости от разрядности, то время суммирования многоразрядных слов существенно сокращается по сравнению с последовательным межсекционным переносом

Многорежимный буферный регистр (МБР)

содержит восемь D – триггеров-защелок, имеющих выходные буферы на элементах с тремя состояниями, схему управления записью и считыванием информации и схему формирования запроса прерывания.

Рассматриваемый регистр обладает универсальными возможностями: он может использоваться в качестве буферного регистра для выхода на магистраль, формирования двунаправленных магистралей, построения адаптеров параллельного интерфейса.

В зависимости от уровней управляющих сигналов МБР может работать в двух режимах: входном и выходном. Это позволяет создавать с помощью МБР двунаправленные магистрали, Если на входе ВР единица, то МБР работает в выходном режиме и выходные буферы открыты, т.е. МБР выдает информацию в выходные шины. Если на входе С - единица, на выходе ВР - нуль и выбран данный МБР, т.е. на входе ВК1 - нуль, а на входе ВК2 - единица, то МБР работает во входном режиме, т.е. выполняется запись в МБР с входных шин D, выходные буферы закрыты и на выход информация не выдается.

Когда МБР находится во входном режиме (сигнал ВР – нуль), сигнал С может использоваться для синхронной записи данных в информационные триггеры и установки триггера в прерывающее состояние. Время цикла МБР составляет 50 нс.

Блок приоритетных прерываний. БПП служит для выработки сигнала запроса на прерывание в процессорной системе. При установки системы в исходное состояние низким уровнем сигнала (“Уст. 0”) триггер запроса на прерывание вырабатывает сигнал прерывания ЗП. Для организации системного сброса этот триггер устанавливается в непрерывающее состояние подачи сигнала R, при этом одновременно сбрасываются информационные триггеры. Сигнал ЗП позволяет подавать сигнал R непосредственно на входы R0

– R7

микросхемы БПП.

Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами.

Описание структурной схемы микропроцессора.

В состав МП (рис. 1) входят арифметическо-логическое устройство, устройство управление и блок внутренних регистров.

Арифметическо-логическое устройство

состоит из двоичного сумматора со схемами ускоренного переноса, сдвигающего регистры и регистров для временного хранения операндов. Обычно это устройство выполняет по командам несколько простейших операций: сложение, вычитание, сдвиг, пересылку, логическое сложение (ИЛИ), логическое умножение (И), сложение по модулю 2.

Устройство управления

управляет работой АЛУ и внутренних регистров в процессе выполнения команды. Согласно коду операций, содержащемуся в команде, оно формирует внутренние сигналы управления блоками МП. Адресная часть команды совместно с сигналами управления используется для считывания данных из определенной ячейке памяти или для записи данных в ячейку. По сигналам УУ осуществляется выборка каждой новой, очередной команды.

Блок внутренних регистров

БВР, расширяющий возможности АЛУ, служит внутренней памятью МП и используется для временного хранения данных и команд. Он также выполняет некоторые процедуры обработки информации.

На рисунке (2) приведена более подробная структурная схема однокристального МП. Здесь блок внутренних регистров содержит регистры общего назначения и специальные регистры: регистр-аккумулятор, буферный регистр адреса, буферный регистр данных, счетчик команд, стека, признаков.

Регистры общего назначения

(РОН), число которых может изменятся от 4 до 64, определяют вычислительные возможности МП. Их функция – хранение операндов. Но могут выполнять также и роль регистров. Все РОН доступны программисту, который рассматривает их как сверхоперативное запоминающее устройство.

Регистр – аккумулятор

(“накопитель”), предназначен для временного хранения операнда или промежуточного результата действий производимой в АЛУ. Разрядность регистра равна разрядности информационного слова.

Буферный регистр адреса

служит для приема и хранения адресной части выполняемой команды. Возможное количество адресов, определяется разрядностью регистра.

Буферный регистр данных

используется для временного хранения выбранного из памяти слова перед передачей его во внешнюю шину данных. Его разрядность определяется количеством байт информационного слова.

Счетчик команд

содержит адрес ячейки памяти, в которой помещены байты выполняемой команды.

Регистр команд

принимает и хранит код очередной команды, адрес которой находится в счетчике команд. По сигналу УУ в него передается из регистра хранимая там информация.

Регистры стека

делятся на стек и указатель стека. В МП стек – набор регистров, хранящих адреса команд возврата при обращении к подпрограммам или состояние внутренних регистров при обработке прерываний. Стек может быть выполнен не только на внутренних регистрах МП, составляя его часть, но и находиться в ОЗУ, занимая там отведенную для него зону. В последнем случае для обращения к нему необходим специальный регистр – указатель стека.

Указатель стека

хранит адреса последней занятой ячейки стека, которую называют вершиной. Содержащее в указателе число указывает, где находится вершина стека. Когда в стек записывается очередное слово, то число в указателе стека соответственно увеличивается. Извлечение слова из стека сопровождается, наоборот, уменьшением числа, заполняющего указатель стека. Кроме такой процедуры предусматривается возможность считывания без разрушений содержимого любой ячейки стека при неизменном числе, хранимом в указателе стека.

Регистр признаков

представляет собой набор триггеров – флажков. В зависимости от результатов операций, выполняемых АЛУ, каждый триггер устанавливается в состояние 0 или 1. Флажковые биты, определяющие содержимое регистра, индицируют условные признаки: нулевого результата, знака результата, перевыполнения и т. п. Эта информация, характеризующая состояние процессора, важна для выбора дальнейшего пути вычислений.

Рассмотрим более подробно основные части микропроцессора (рис. 2).

Внутренняя шина данных

соединяет собой основные части МП.

Шиной

называют группу линий передачи информации, объединенных общим функциональным признаком. В микропроцессорной схеме используется три вида шин: данных, адресов и управления.

Разрядность внутренней шины данных т. е. количество передаваемых по ней одновременно (параллельно) битов числа соответствует разрядности слов, которыми оперирует МП. Очевидно, что разрядность внутренней и внешней шин данных должна быть одной и той же. У восьмиразрядного МП внутренняя шина данных состоит из восьми линий, по которым можно передавать последовательно восьмиразрядные слова – байты. Следует иметь в виду, что по шине данных передаются на только обрабатываемые АЛУ слова, но и командная информация. Следовательно, недостаточно высокая разрядность шины данных может ограничить состав (сложность) команд и их число. Поэтому разрядность шины данных относят к важным характеристикам микропроцессора – она в большей мере определяет его структуру (числа разрядов указаны на рисунке в скобках рядом с названиями блоков).

Шина данных МП работает в режиме двунаправленной передачи, т. е. по ней можно передавать слова в обоих направлениях, но не одновременно. В этом случае требуется применение специальных буферных схем и мультиплексного режима обмена данных между МП и внешней памятью. Мультиплексный режим

(от английского слова multiple – многократный, множественный), иногда называемый многоточечным

, - режим одновременного использования канала передачи большим числом абонентов с разделением во времени средств управления обменом.

Мультиплексор

– устройство, которое выбирает данные от одного, двух (или более) входных информационных каналов и подает эти данные на свой выход. Схема мультиплексора состоит из двухвходовых логических элементов И – ИЛИ, управляемых распределителем импульсов. Промышленностью выпускаются мультиплексоры, которые могут входить в состав , а также в виде отдельных БИС (например, восьмивходовый одноразрядный; двухвходовый четырехразрядный; трехвходовый четырехразрядный и др.).

Демультиплексор

– устройство, выполняющее противоположную мультиплексору функцию, - подает данные, подводимые к его входу, на один (или более) выходной информационный канал.

Мультиплексоры и демультиплексоры позволяют компоновать из микропроцессорных элементов микроЭВМ для любой длины машинного слова. Предположим, что задача обработки данных заключается в сложении двух операндов, каждый из которых представляет собой восьмиразрядное двоичное число – байт.

Восьмиразрядное арифметически – логическое устройство

выполняет все арифметические и логические операции. На первый вход АЛУ поступает байт из восьмиразрядного аккумулятора

, а на второй вход – из восьмиразрядного промежуточного регистра

. Результат сложения указанных двух байтов передается с выхода АЛУ через внутреннюю шину данных в аккумулятор. Такая организация удовлетворяет одноадресной организации микропроцессора. Для нее характерно то, что один из операндов, участвующих в обработке, всегда находится в аккумуляторе, адрес которого задан неявно. Поэтому при выполнении операции сложения двух операндов требуется указывать только один адрес – второго операнда, содержащегося, например в одном из восьми регистров общего назначения

(РОН). К АЛУ подключены регистр признаков

, предназначенный для хранения и анализа признаков результата операции, и схема десятичной коррекции

(на рис. 2 не показана), позволяющая проводить обработку данных в двоично-десятичном коде.

В состав микропроцессора входят также указатель стек, счетчик команд, буферный регистр адреса, ОЗУ. Первые два РОН – регистры W и Z – предназначены для кратковременного хранения данных во время выполнения команды (эти регистры недоступны программисту), остальные шесть РОН – регистры B, C, D, E, H и L – служат ячейками внутренней памяти, называемой сверхоперативным запоминающим устройством

(СОЗУ). В них хранятся операнды, подлежащие обработки в АЛУ, результаты обработки данных, выполненных в АЛУ, и управляющие слова. В каждом регистре помещается один байт. Обращение к РОН – адресное. Попарное расположение регистров B и C, D и E, H и L дает возможность проводить обработку двухбайтовых слов, называемую обработкой “удвоенной точности”. Обмен данными с РОН (считывание и запись информации) осуществляется через мультиплексор

, причем требуемый регистр выбирается с помощью селектора регистров по сигналу УУ

.

В левой части рис. 2 расположены регистр команд, дешифратор кода операции и УУ (хотя дешифратор относится к УУ, он нарисован отдельно для большей наглядности). Стековый регистр адреса на рисунке отсутствует, так как стек представляет собой определенную зону ОЗУ.

Обмен информацией между регистрами и другими блоками микропроцессора производится через внутреннюю шину данных, причем передачи команд и данных разделены во времени. Связь с внешней шиной данных осуществляется через буферный регистр данных

.

Микропроцессор – это программно-управляемое устройство. Процедура выполняемой им обработки данных определяется программой, т. е. совокупностью команд. Команда делится на две части: код операции и адрес. В коде операции заключена информация о том, какая операция должна быть выполнена над данными, подлежащими обработке. Адрес указывает место, где расположены эти данные (в регистрах общего назначения микропроцессора, т. е. во внутренней или внешней памяти). Слово данных, подвергаемое обработке, представляет один байт. Команда может состоять из одного, двух или трех байтов, последовательно расположенных в памяти.

Первый байт команды содержит код операции. Считанный в начале интервала выполнения команды, называемого циклом команды, ее первый байт поступает по внутренней шине данных в регистр команд, где хранится в течение всего цикла. Дешифратор кода операции дешифрует содержимое регистра команд – определяет характер операции и адреса операндов. Эта информация подается в УУ, которое вырабатывает управляющие сигналы, направляемые в блоки микропроцессора, участвующие в выполнении данной команды.

В том случае, когда код операции непосредственно указывает адрес данных – объекта обработки, операция начинается сразу после считывания первого байта команды. Если же в команде содержится более одного байта, то остальные байты, несущие информацию об адресе ячейки памяти, где хранятся данные, передаются либо в буферный регистр адреса, либо в один из РОН только после завершения всей процедуры считывания команды или, иначе говоря, после получения полной информации о местонахождении операндов и о том, какая операция должна выполнятся, начинается операция.

Рассмотрим пример выполнения операции сложения двух операндов. Первый операнд хранится в аккумуляторе, второй в одном из РОН (его адрес указан в команде), откуда он передается в промежуточный регистр. Согласно коду операции АЛУ суммирует поступающие на его вход байты и выдает результат, который фиксируется в аккумуляторе. Этот результат можно использовать при дальнейших этапах обработки.

Наряду с многокристальными и однокристальными МП используются секционированные или разрядно-модульные МП. Основной их отличительной особенностью является то, что каждый модуль предназначен для обработки нескольких разрядов машинного слова, а слово в целом обрабатывается группой модулей или секций, соединенных между собой.

Основные микропроцессорные комплекты и их функциональный состав.

Наибольшее распространение получили микропроцессоры, управляемые по программам или микропрограммам. Такие МП строятся на базе ЭСЛ, ТТЛШ, КМОП, И2

Л и других распространенных элементов. Современные микропроцессоры представляют собой набор БИС, соединенных между собой определенным образом, которые составляют так называемые микропроцессорные комплекты (МПК).

За последние годы разработано значительное количество различных МПК. Сравнительные обобщенные характеристики некоторых из них приведены в табл. 1.

Таблица 1.

| Серия МПК |

технология |

разрядность |

быстродействие |

Число РОН |

Мощность потребл. Вт. |

Число ИС в базовом МПК |

Число ИС в МПК |

Числоисточников питания |

| К589 |

ТТЛШ |

2 |

1000 |

11 |

2,15 |

2 |

8 |

1 |

| К1800 |

ЭСЛ |

4 |

3000 |

1 |

3,23 |

2 |

4 |

2 |

| К1801 |

n-МОП |

6 |

550 |

8 |

1,0 |

1 |

1 |

1 |

| К1802 |

ТТЛШ |

4 |

1400 |

16 |

2,2 |

2 |

6 |

1 |

| К1804 |

ТТЛШ |

4 |

550 |

16 |

2,05 |

2 |

8 |

1 |

Микропроцессорные комплекты изготовляют в виде секционных БИС с возможностью наращивания. Исключение составляет БИС КР580ИК80А – восьмиразрядный МП, в котором можно увеличить разрядность обрабатываемых данных путем двойного пересчета. В состав секционных МПК входят как правило, п

-разрядная МП секция, предназначенная для обработки информации и временного хранения результатов, схема микропрограммного УУ, а также БИС, выполняющие функции по обработке прерываний программы, синхронизации и связи с периферийными устройствами.

Возможность наращивания разрядности обрабатываемой информации и применение микропрограмм обеспечивают гибкость и широкую сферу применения секционных МПК, так как разработчик аппаратуры сам может определять набор команд.

В структуре МПК можно выделить операционную и управляющую части. Операционная часть поводит логическую обработку информации, управляющая часть декодирует команды и формирует сигналы, необходимые для выполнения той или иной операции. Каждая команда представляет собой небольшую программу, состоящую из элементарных операций. Последовательность таких команд называется микропрограммой. Очередность команд, в соответствии с которой работает управляющая часть МП, называется программой.

Первые МП строились на р

-канальных МОП-транзисторах, поэтому имели невысокое быстродействие. В дальнейшем появились МП, в которых использовались п

-канальные МОП-транзисторы и биполярные интегральные структуры (И2

Л, ТТЛШ и ЭСЛ), что привело к значительному увеличению быстродействия.

Количество различных операций, выполняемых некоторыми МП, доходит до 100, причем в них предусматриваются операции с двойной длиной слова и побайтовой обработкой информации. В процессе развития наряду с МП, имеющими фиксированный список команд, появились МП с микропрограммным управлением, которое позволяет изменять список команд и алгоритмы управления. Это увеличивает гибкость процессора и упрощает реализацию последовательности относительно сложных микрокоманд.

Важнейший параметр МП - быстродействие. В настоящее время диапазон быстродействия МП - от десятков тысяч до 1- 3 млн. коротких операций.

отечественная промышленность выпускает секционированные микропроцессорные комплекты серий К-589, КР-1802, КР-1804, К18-00 и др.

Секционированный микропроцессорный комплект БИС серии К589.

Микропроцессорный комплект БИС серии к 589 состоит из восьми микросхем, выполненных по ТТЛШ-технологии , блоков микропрограммного управления (БМУ) К 589ИК01; центрального процессорного элемента (ЦПЭ) К589ИК02; схем ускоренного переноса (СУП) К89ИК03 и многорежимного буферного регистра (МБР) К589ИР12; блока приоритетных прерываний (БПП) К589ИК14; шинных формирователей без инверсий (ШФ) К589АП16 и с инверсией (ШФИ) К589АП16; схемы синхронизации и управления (МСУ) К589ХЛ4.

Комплект обеспечивает построение автономных микро- и мини- ЭВМ, контроллеров, устройств автоматики с различной архитектурой благодаря модульности структуры, возможности параллельного наращивания микропрограммного управления, совместимости с ТТЛ-транзисторами серии к155 и др.

Микросхемы герметизированы в пластмассовых корпусах с вертикальным расположением выводов.

Соединяя параллельно несколько МП, можно получить процессор с требуемой длиной слова. Для реализации 16-разрядного процессора, содержащего УУ, шины и микропрограммное ЗУ, требуется примерно 20 БИС и 10 ИС. Такой процессор заменяет эквивалентную систему на ТТЛ ИС среднего уровня интеграции, имеющую более 200 корпусов. Центральный микропроцессор (ЦП) в нем состоит из восьми микросхем ЦПЭ, одного БМУ, ЗУМК. На рис 3 показана структурная схема такого процессора. Микропрограмма, находящаяся в управляющей памяти, после выключения питания устанавливает ЦП в исходное состояние и осуществляет выборку и выполнение команд. Разрядность слова микропрограммной памяти определяется числом и разрядностью микроинструкций.

Центральный процессорный элемент имеет шесть групп входов и выходов, по которым происходит связь с другими схемами. Четыре из них (В, М, А, D) используются преимущественно для связи с внешней памятью и устройствами ввода – вывода. Группа выводов F0

– F6

используется для управления работой ЦПЭ, а входы К – для маскирования информации для занесения константы.

Блок микропрограммного управления. Он имеет восемь входов команды К (макрокоманды). Таким образом, информация о коде операции определяется восемью разрядами, т. е. максимальное число макрокоманд 256. Число разрядов микрокоманды, требуемое для управления БМУ, равно: семь разрядов УАО – УА6 – для управления выработкой перехода к следующему адресу микрокоманды и четыре УФ0 – УФ3 – для управления схемой выработки признаков условных переходов. Таким образом, для управления ЦПЭ и БМУ необходимо 19 разрядов. Кроме этих микроинструкций необходимы дополнительные микроинструкции для управления памятью, вводом – выводом и т. д.

Данные в АЛУ поступают из памяти из устройства ввода информации и одаются в регистр-аккумулятор. В него поступают также результаты операций, выполняемых в АЛУ. После завершения операций данные посылаются в память или в устройства вывода информации.

Устройство управления управляет операциями в соответствии с содержанием команд, которые считываются из внешнего ЗУ, и помещаются в регистр команд. Адрес очередной команды обычно определяется счетчиком команд. В качестве регистра и счетчика команд используются внутренние регистры ЦПЭ.

Связь с ЗУ осуществляется через регистр адреса памяти и регистр данных памяти, выходы которых соединены с соответствующими адресными и информационными сигналами. Разрядность адреса памяти определяет адресуемое поле памяти. Часть регистров МП используется в качестве сверхоперативной памяти, в которой хранятся промежуточные результаты вычислений. Это позволяет повысить быстродействие процессора.

Для обеспечения контроля за состоянием регистров при выполнении операций используются регистры состояний блока микропрограммного управления (БМУ). Триггеры этих регистров (флажки) индицируют переполнение регистров ЦПЭ, нулевое содержание аккумуляторов, знак его содержимого и другие состояния. Эта информация используется для организации условных переходов в микропрограммах.

Синхронизация работы отдельных узлов процессора осуществляется одной или несколькими сериями тактовых импульсов. Для реализации одной команды необходимо несколько периодов тактовых импульсов. Командный цикл состоит из цикла выборки, во время которого вырабатывается адрес команды и по нему вырабатывается команда и считываются в регистр данные из памяти, и цикла , исполнительного, во время которого в устройстве управления команда дешефруется и процессор исполняет ее.

Рассмотрим подробно структуру и основные характеристики отдельных БИС комплекта серии К589.

Центральный процессорный элемент предназначен для логической и арифметической обработки информации, приема, хранения и выдачи оперативной информации, а также для формирования адресов памяти. Он представляет собой двухразрядную микропроцессорную секцию со структурой, обеспечивающей практически неограниченные возможности объединения кристаллов ЦПЭ по горизонтали с целью увеличения разрядности процессора.

Основная особенность ЦПЭ – большое число шин: три входные и две выходные с адресным регистром данных это обеспечивает возможность выдачи данных и адресов в память одновременно. Назначение шин ЦПЭ – пересылка байтов, тестирование битов, ввод – вывод информации во внутренние регистры.

Формирователи выходных шин выполнены на элементах с тремя состояниями, что существенно упрощает подключение УПЭ к магистрали. Шина микрофункций управляет работой секций, выбирая операнды и операции, которые должны выполнятся в АЛУ. ЦПЭ выполняет свыше 40 логических и арифметических операций. Секция выдает сигналы ускоренного переносы. Кроме того, она снабжена независимыми линиями входа и выхода переноса, входа и выхода сдвигаемого кода.

В состав ЦПЭ входят АЛУ, 11 сверхоперативных регистров, два мультиплексора (А и В), аккумулятор, регистр адреса памяти, дешифратор микрофункций.

Информация на ЦПЭ поступает по трем группам независимых входов М, В и К из основной памяти, устройств ввода – вывода, памяти микропрограмм. Информация, поступающая на ЦПЭ, хранится в 11 регистрах R0

– R9

, T , а также в накапливающем регистре АС или в регистре адреса памяти. Через мультиплексоры А и В информация передается в АЛУ. Регистры R0

- R9

и Т выполняют функции сверхоперативного запоминающего устройства и могут быть использованы как счетчики. Информация с регистров через мультиплексор А поступает в АЛУ, а с выхода АЛУ – снова на регистры. Аккумулятор служит для хранения результата операций АЛУ. Информация с выхода аккумулятора поступает на вход АЛУ или через выходной усилитель – буфер – может выдаваться на выходную магистраль для передачи в основную память или на устройство ввода – вывода. Через мультиплексоры А и В она может подаваться на один из двух входов АЛУ. На входы мультиплексора А поступают данные со входов М, регистров R0

– R9

, Т и аккумулятора, а на входы мультиплексора В – информация со входов В , К и аккумулятора. При этом производится маскирование информации входов В и АС данными на входах К. результат операций, выполняемых в АЛУ, может хранится в R0

– R9

и аккумуляторе.

При операции сдвига в право используют вход СП1 и выход СП0, для организации последовательного переноса - вход С1 и выход С0. Наличие выходов Х и У обеспечивает организацию ускоренного (сквозного) переноса между микросхемами ЦПЭ. При неарифметических операциях схемы переноса используют для выполнения логического ИЛИ всех разрядов слова с учетом маскирования по входам К. Входом К пользуются при арифметических операциях для маскирования полей и отдельных разрядов обрабатываемых слов. Через входы К в ЦПЭ могу подаваться константы из памяти микропрограмм. Обычно регистр адреса используется для хранения и пересылки адреса команд в основную память. В этом случае информация с АЛУ через отдельный выход поступает на регистр памяти. В каждом микрокомандном цикле на входы F поступает микроинструкция (часть поля микрокоманды,), которая дешифруется и определяет выполнение необходимы операций ЦПЭ. Микроинструкция F0-F6 разбита на два поля F и R- группы. F -группы (F4-F0) определяет код операции, регистровая R- группа (F0-F3) - адрес регистров.

На рис. 4 показан вариант соединения БИС ЦПЭ с последовательным переносом, осуществляемым с помощью БИС ускоренного переноса. Цикл обработки ЦПЭ составляет 100 нс.

Блок микропрограммного управления предназначен для управления последовательностью выборки микрокоманд из управляющей памяти (ЗУМК) и выполняет следующие функции: управление регистром адреса микрокоманды; выборку очередной микрокоманды с учетом содержимого РАМК; хранение и выдачу признаков; управление микропрограммными прерываниями. В состав БМУ (рис. 5) входят: девятиразрядный регистр адреса микрокоманд и соответствующая магистраль; схема формирования очередного адреса; выходные буферы адреса микрокоманды на элементах с тремя состояниями; триггеры признаков (C, Z, Ф); регистр команды; выходной буфер флажков.

Формирование адреса очередной микрокоманды выполняется с помощью условных и безусловных переходов. В каждой текущей микрокоманде содержится поле микроинструкции БМУ, предназначенной для формирования адреса следующей микрокоманды. Адреса микрокоманды (всего 512) образуют матрицу (страницу), состоящую из 32 строк и 16 столбцов. Каждый адрес определяется номером той строки и того столбца, на пересечении которых он находится. Под адрес строки отводится пять разрядов (МА8

– МА4

), а под адрес столбца четыре разряда (МА3

– МА0

). Девятиразрядный адрес микрокоманды, выработанный логикой следующего адреса, загружается в регистр адреса микрокоманд, а из него выдается в память микрокоманд по десяти выходным шинам.

Блок микропрограммного управления обеспечивает хранение текущего значения на выходе переноса ЦПЭ (С0, СП0) и управляет информацией на входе переноса (С1, СП1). С помощью двух групп микроинструкций осуществляется управление признаками - установка и их выдача. Схема обработки признаков содержит три триггера: С и Z и триггер - защелку Ф, в которой запоминается текущее состояние выхода переноса ЦПЭ. Логическая схема признаков совместно со схемой переноса ЦПЭ используется для выполнения арифметических и сдвиговых операций.

Сигнал в двоичном коде на входах УА используется для формирования адресов строки и столбца и вида микроопераций, выполняемой БМУ. По четырем микроинструкциям производятся безусловные переходы, по остальным - условные. Для формирования адреса следующей микрокоманды при безусловных переходах используется адрес текущей микрокоманды, который хранится в регистре адреса и ряд битов микроинструкции УА0

-УА6

: при условных переходах - адрес текущей (предыдущей) микрокоманды и содержимое регистров С, Z или Ф либо код старших разрядов К4

-К7

. Для выработки следующего адреса микрокоманды по содержимому данных на шинах К4

-К7

используется часть адреса текущей микрокоманды и несколько разрядов кода на шинах УА.

Управление схемой обработки признаков (C, Z и Ф) осуществляется с помощью микроинструкции на входах УФ0

– УФ3

. Информация на входе Ф записывается в триггер Ф и затем в триггер С или Z. По входу ЗМ дается разрешение на запись информации со входов К в регистр адреса микрокоманд. Разрешение на прерывание выдается с выходной шины СРП при микроинструкции ПЕРЕХОД В НУЛЕВУЮ СТРОКУ, что означает конец выполнения микропрограммы (команды). Обычно сигнал с шины СРП подается на входную шину СРП блока приоритетного прерывания. Этот блок может ответить на прерывание выдачей сигнала подтверждения прерывания, что блокирует выдачу следующего выбранного адреса строки из БМУ. Тогда при выдаче нового адреса микрокоманды на линию адреса строки можно подавать адрес извне минуя БМУ, что позволяет перевести микропрограмму на программу обработки прерывания. Измененный адрес строки, переданный на адресные линии микрокоманд, не изменяет содержимого регистра адреса микрокоманд. Таким образом, последующая функция перехода будет использовать адрес строки в регистре адреса микрокоманды, а не измененный адрес строки.

Цикл БМУ составляет 85 нс. Имеется возможность адресации 512 микрокоманд (предусмотрена возможность наращивания числа адресуемых микрокоманд). Корпус микросхемы типа ДИП с 40 выводами.

Схема ускоренного переноса (СУП)

предназначена для формирования групповых переносов при совместном использовании с ЦПЭ в многоразрядных сумматорах. Микросхема позволяет объединить до восьми ЦПЭ, т. е. образовать 16-разрядный сумматор.

Схема имеет 17 информационных входов, 8 информационных выходов и один управляющий вход, позволяющий управлять выходом самого старшего переноса.

В каждом ЦПЭ формируются сигналы подготовки сквозного переноса, которые подаются в схему ускоренного переноса, а она в свою очередь вырабатывает сигналы переносов, поступающие в ЦПЭ. Если в каждом разряде 1, то сигнал подготовки также 1 и через данную секцию происходит перенос от младшей к старшей. Так как схема ускоренного переноса генерирует сигналы переносов во все ЦПЭ одновременно вне зависимости от разрядности, то время суммирования многоразрядных слов существенно сокращается по сравнению с последовательным межсекционным переносом

Многорежимный буферный регистр (МБР)

содержит восемь D – триггеров-защелок, имеющих выходные буферы на элементах с тремя состояниями, схему управления записью и считыванием информации и схему формирования запроса прерывания.

Рассматриваемый регистр обладает универсальными возможностями: он может использоваться в качестве буферного регистра для выхода на магистраль, формирования двунаправленных магистралей, построения адаптеров параллельного интерфейса.

В зависимости от уровней управляющих сигналов МБР может работать в двух режимах: входном и выходном. Это позволяет создавать с помощью МБР двунаправленные магистрали, Если на входе ВР единица, то МБР работает в выходном режиме и выходные буферы открыты, т.е. МБР выдает информацию в выходные шины. Если на входе С - единица, на выходе ВР - нуль и выбран данный МБР, т.е. на входе ВК1 - нуль, а на входе ВК2 - единица, то МБР работает во входном режиме, т.е. выполняется запись в МБР с входных шин D, выходные буферы закрыты и на выход информация не выдается.

Когда МБР находится во входном режиме (сигнал ВР – нуль), сигнал С может использоваться для синхронной записи данных в информационные триггеры и установки триггера в прерывающее состояние. Время цикла МБР составляет 50 нс.

Блок приоритетных прерываний. БПП служит для выработки сигнала запроса на прерывание в процессорной системе. При установки системы в исходное состояние низким уровнем сигнала (“Уст. 0”) триггер запроса на прерывание вырабатывает сигнал прерывания ЗП. Для организации системного сброса этот триггер устанавливается в непрерывающее состояние подачи сигнала R, при этом одновременно сбрасываются информационные триггеры. Сигнал ЗП позволяет подавать сигнал R непосредственно на входы R0

– R7

микросхемы БПП.

Шинные формирователи. Блоки шинных формирователей предназначены для подключения модулей к магистрали. Типичная задержка на ШФ и ШФИ - 20нс, корпус схемы типа ДИП с 16 выводами.

|