1 Техническое задание на разработку проекта

Исходные данные для проектирования

Назначение устройства

Устройство, разработка которого проводится в данной работе, - контроллер системы автоматизации. В качестве реализуемых на его основе функций можно назвать следующие: получение данных от датчиков состояния объекта управления, формирование управляющих воздействий согласно решаемым задачам, обмен информацией с другими контроллерами и центральной ЭВМ. Также в этот список можно включить и такие внутренние сервисные функции как самодиагностика и контроль хода выполнения программы – выявление ситуаций “зависания”.

В проекте не рассматриваются процессы непосредственного управления объектом. Поэтому основной задачей контроллера будет прием данных от внешнего источника, преобразование их в нужный формат и передача дальше по цепочке. То есть контроллер можно рассматривать как некий “информационный” ретранслятор, снабженный функциями контроля и самодиагностики.

Контроллер принимает данные в виде пакетов в соответствии с протоколом X-Modem, обеспечивающим проверку возникновения ошибок передачи и повторный запрос пакета в случае их возникновения. Реализуемый интерфейс приема – ИРПР-М.

Информация буферизуется и передается дальше по одному байту без контроля ошибок также с использованием интерфейса ИРПР-М. Дополнительно с помощью программируемого таймера контроллер производит проверку состояния ПЗУ (подсчет контрольной суммы) и анализ хода выполнения программы. В случае несовпадения контрольной суммы либо зависания одной из задач выключается индикатор нормальной работы, и процесс останавливается до вмешательства оператора.

1.1.2 Характеристики интерфейса ИРПР-М

Интерфейс ИРПР-М является унифицированной системой связей и сигналов и обеспечивает единые способы обмена информацией при соединении корреспондентов посредством кабеля. Интерфейс ИРПР-М может быть использован при построении сосредоточенных модульных систем обработки данных. По классификационным признакам интерфейс ИРПР-М является межблочным, асинхронным, параллельным, однонаправленным, радиальным интерфейсом. Единицей обмена данными для интерфейса является байт или слово. Максимальное удаление двух взаимодействующих компонент – 15 метров. Максимальное число линий связи – 40. Минимальный набор линий связи приведен в таблице 1.1

Таблица 1.1 - Сигналы интерфейса ИРПР-М

| Сигнал |

Активный

Уровень

|

Инициатор

сигнала

|

Комментарий |

| -ACKNLG |

Низкий |

Приемник |

Запрос очередного байта данных |

| BUSY |

Высокий |

Приемник |

Высокий уровень на линии сигнализирует о неготовности приемника к обмену |

| -STROBE |

Низкий |

Передатчик |

Строб данных |

| DATA |

- |

Передатчик |

Восемь (шестнадцать) линий данных |

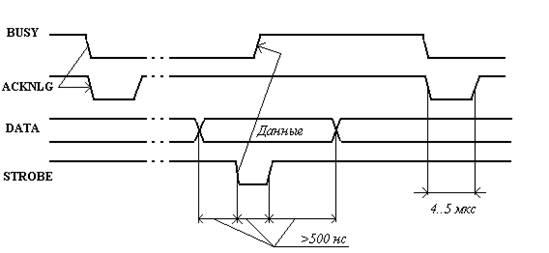

Временные диаграммы, объясняющие обмен информацией по линиям интерфейса, представлены на рисунке 1.1.

Рисунок 1.1 – Временные диаграммы интерфейса ИРПР-М

1.1.3 Структура сообщений

Прием данных осуществляется в соответствии с протоколом X-Modem. Пакет информации представляет собой последовательность из 132 байт. Структура пакета:

Заголовок пакета. В качестве заголовка выступает код 01h (SOH).

Два байта – номер пакета. Первый байт – собственно номер, а второй его дополнение (для контроля ошибок).

Тело пакета – 128 байт.

Байт контрольной суммы. Контрольная сумма охватывает номер пакета и тело пакета.

Для сопровождения обмена используются служебные символы, представленные в таблице 1.2.

Таблица 1.2 – Служебные символы протокола X-Modem

| Символ |

Шестнадцатиричный код |

Назначение |

| SOH |

01h |

Символ начала пакета |

| ACK |

06h |

Подтверждение приема |

| NAK |

15h |

Отрицание приема |

| EOT |

04h |

Завершение обмена |

| CAN |

18h |

Аварийное завершение обмена |

Процесс обмена осуществляется следующим образом: Приемник посылает передатчику подряд два сигнала NAK. В ответ передатчик начинает посылку пакетов. После приема каждого пакета приемник анализирует правильность передачи и посылает передатчику символ ACK – подтверждение приема. Если при подсчете контрольной суммы обнаружена ошибка, то вместо сигнала ACK передается NAK – запрос на повторную передачу пакета. Последовательность пакетов передатчик завершает символов EOT, который приемник подтверждает сигналом ACK. Если при установке связи передатчик не ответил на запрос информации (два сигнала NAK), то приемник продолжает посылать запрос NAK с интервалом 10 секунд. Может быть послано до десяти запросов NAK.

Передача информации производится посимвольно. Причем данные посылаются блоками по 256 байт. В начале каждого блока располагается четыре байта, несущие информацию о текущем времени контроллера. Данные блоки формируются в отдельном участке памяти – буфере передатчика и посылаются п мере готовности. За формированием информационных блоков следит специальная задача.

Структура и алгоритм функционирования контроллера.

1.2.1 Структурная схема контроллера

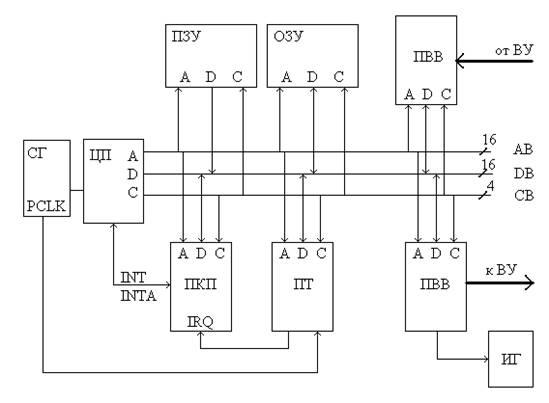

Структурная схема контроллера представлена на рисунке 1.2.

Элементы, входящие в схему:

СГ – системный генератор.

ЦП – центральный процессор.

ПЗУ – постоянное запоминающее устройство.

ОЗУ – оперативное запоминающее устройство.

ПКП – программируемый контроллер прерываний.

ПТ – программируемый таймер.

ИГ – индикатор готовности.

ПВВ – порт ввода-вывода.

Рисунок 1.2 - Структурная схема контроллера

Системная шина контроллера состоит из трех составляющих: шины адреса (AB), шины данных (DB), шины управления (CB).

Индикатор готовности информирует о нормальной работе устройства – в случае возникновения ошибок индикатор гасится.

Диаграммы состояний основных процессов

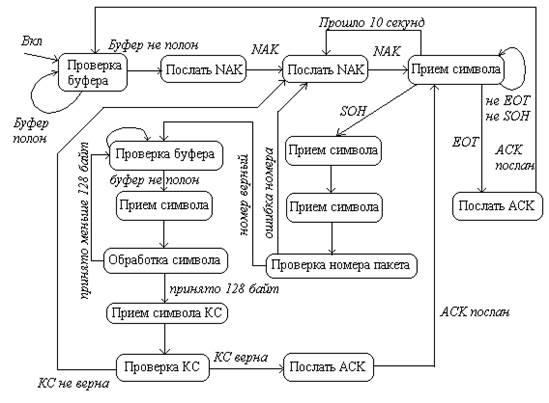

Диаграмма состояний процесса приема, показанная на рисунке 1.3, наглядно иллюстрирует работу контроллера при приеме данных от внешнего устройства.

Так как прием информации осуществляется пакетами, то в основе схемы лежит диаграмма состояний при использовании протокола X-Modem.

Рисунок 1.3 - Диаграмма состояний процесса приема данных

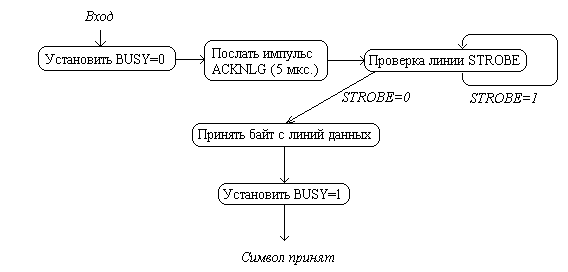

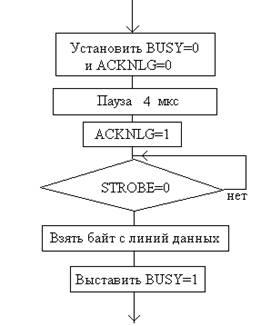

Более подробно состав блока “Послать символ” представлен на рисунке 1.4.

Рисунок 1.4 – Состав блока “Принять символ”

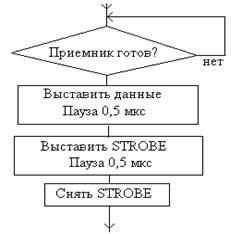

Содержание блока “Послать символ” раскрыто на рисунке 1.5.

Рисунок 1.5 – Состав блока “Послать символ”.

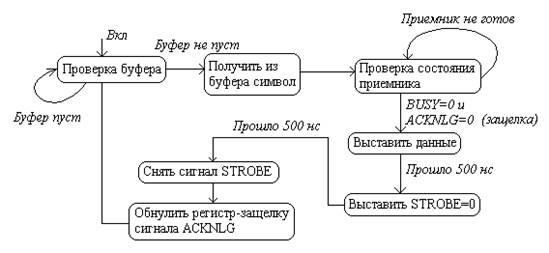

На рисунке 1.6 показана диаграмма процесса передачи информации. Передача ведется по одному байту без контроля ошибок.

На рисунке событие “Прошло 500 нс” означает выдержку необходимой паузы для формирования сигнала. Включение передатчика происходит при наличии флага готовности буфера передачи. Поэтому проверка буфера включает в себя и проверку состояния флага.

Рисунок 1.6 - Диаграмма состояний процесса передачи данных.

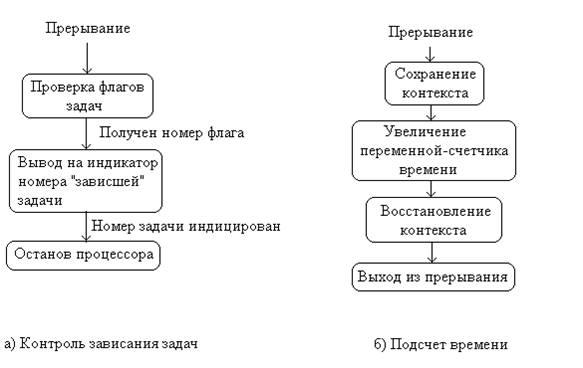

Диаграмма состояний процесса самодиагностики показана на рисунке 1.7.

Подсчет контрольной суммы ПЗУ (КС) ведется в цикле. В случае несовпадения рассчитанного значения с контрольными данными происходит останов процессора. Блок “Подсчет КС” обозначает циклический процесс по суммированию по модулю 256 содержимого ячеек ПЗУ.

Рисунок 1.7 - Диаграмма состояний процесса самодиагностики

Диаграмма состояний процесса “службы времени” представлена на рисунке 1.8.

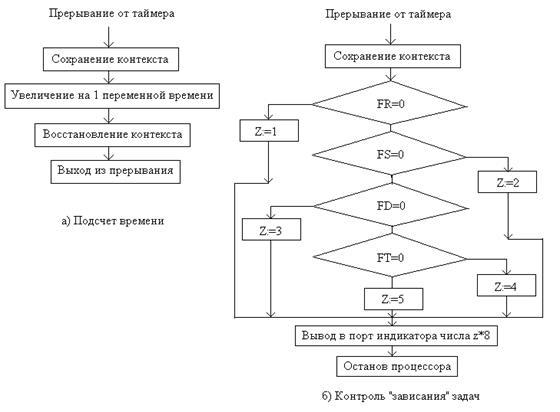

Служба времени решает две задачи. Это контроль зависания задач и формирование переменной, содержащей текущее время от начала работы контроллера. Конторль зависания осуществляется следующим образом. Перед началом каждого цикла прохода подпрограмм диспетчер запускает таймер, работающий в роли одновибратора. Время срабатывания таймера заведомо больше времени одного цикла работы диспетчера. Поэтому, если все задачи отработали успешно, таймер не успеет сработать до следующего перезапуска. Если таймер сработает и вызовет прерывание, то это сигнализирует о “зависании” одной из задач. В данной ситуации требуется немедленно остановить работу процессора. При подсчете времени таймер генерирует импульсы определенной частоты, по которым контроллер прерываний формирует запросы на прерывание для процессора. Обработчик этих прерываний каждый раз наращивает на единицу переменную-счетчик времени.

Рисунок 1.8 - Диаграмма состояний процесса “службы времени”

Разработка аппаратной части контроллера

Обоснование выбора микропроцессора

Шестнадцатиразрядный микропроцессор КР1810ВМ86 обеспечивает возможность эффективной работы с языками высокого уровня, имеет гибкую и мощную систему команд. Может быть использован как 16-ти так и 8-ми разрядный процессор. ВМ86 выполняет операции над битами, байтами, двухбайтовыми словами, действия знаковой и беззнаковой двоичной или десятичной арифметики, в том числе умножение и деление, имеет гибкую структуру аппаратурных и программных прерываний (до 256 типов).

К наиболее важным аппаратурным особенностям К1810ВМ86 относятся: развитая регистровая структура, существенно уменьшающая число обращений к памяти; конвейерный принцип выполнения команд с предварительной выборкой, обеспечивающий максимальную пропускную способность системной магистрали; распределенное микропрограммное устройство управления; мультиплексированная шина адреса-данных; многофункциональное использование выводов, позволяющее адаптировать МП к уровню сложности разрабатываемой системы; способность координировать взаимодействие нескольких процессоров.

Распределение адресного пространства

Микропроцессор К1810ВМ86 позволяет адресовать до 1Мбайт памяти. Так как основной задачей разрабатываемого контроллера является прием информации, преобразование в другой формат и передача ее следующему корреспонденту, то распределение память становится важной задачей. Особенности процессора заставляют выбирать такую структуру памяти, при которой младшие адреса занимает ОЗУ, а старшие – ПЗУ. Поставленная задача не требует реализации полного объема возможной памяти, поэтому используется следующая структура памяти:

· адреса 0000 – 3FFFh соответствуют ОЗУ;

· адреса 4000 – 7FFFh соответствуют ПЗУ.

· Порты ввода-вывода, регистры управления таймера и программируемого контроллера прерывания также имеют фиксированные адреса:

· адреса 0000-0006 соответствуют порту ввода-вывода, предназначенному для приема данных;

· адреса 0008-000Еh соответствуют порту ввода-вывода, предназначенному для передачи данных;

· адреса 0010-0016h соответствуют управляющим регистрам программируемого таймера;

· адреса 0018-001Ah соответствуют управляющим регистрам программируемого контроллера прерываний.

Функциональная схема контроллера

Функциональная схема контроллера приведена в приложении.

Параллельный порт ввода-вывода PPI (DD15) предназначен для обеспечения приема информации в соответствии с протоколом X-Modem. Поэтому необходима двунаправленная связь. Фактически на микросхеме реализовано два интерфейса ИРПР-М. Один из них, для приема байтов информации, имеет следующую организацию:

сигналы DIN

0 - DIN

7 – выводы РА

0 – РА

7;

сигнал STROBEIN

– вывод РС

4;

сигналы BUSYIN

и ACKNLGIN

– выводы РС

0 и РС

1 соответственно.

При приеме байта, он поступает на линии порта А (сигналы DIN

0 – DIN

7). Для передачи управляющих символов используется порт В. При этом служебные сигналы подключаются к следующим линиям:

сигнал STROBEOUT

– вывод РС

2;

сигналы BUSYOUT

и ACKNLGOUT

– выводы РС

5 и РС

6 соответственно.

Для передачи информации используется параллельный порт ввода-вывода PPI (DD16) На нем также реализован интерфейс ИРПР-М.Данные выдаются через порт А. Сигнал STROBE поступает в линию связи через нулевой разряд порта В. Сигналы готовности приемника BUSY и ACKNLG поступают в порт С (разряды 1 и 0 соответственно). Так как импульс ACKNLG имеет длительность около 5 мкс, то его программная фиксация в режиме параллельной обработки нескольких задач затруднена. Предусмотрена аппаратная защелка этого сигнала с помощью триггера. После получения сигнала ACKNLG триггер программно сбрасывается. Аналогичная схема присутствует и в блоке приема данных.

Индикатор готовности выполнен на дешифраторе DD28. Его адресные входы подсоединены к линиям 4, 5, 6 порта С микросхемы DD16. Регистр в нормальном рабочем режиме управляет индикатором готовности системы, а в случае конфликтной ситуации отображает номер “зависшей” задачи.

Программируемый таймер используется для отсчета интервалов времени для контроля выполнения задач и вызова прерываний для самопроверки контроллера – подсчета контрольной суммы ПЗУ. В качестве счетных импульсов к таймеру подведен сигнал с выхода PCLK системного генератора, имеющий частоту, в два раза меньшую, чем тактовая частота процессора. При частоте процессора 5 МГц таймер отсчитывает импульсы с частотой 2,5 МГц. При этом максимальная задержка, обеспечиваемая таймером равна 26 мс.

Программируемый контроллер прерываний служит для упорядочения запросов на прерывание по приоритету и во времени. В данной схеме обслуживается два прерывания: контроль прохождения контрольной точки задачами и самодиагностика. Запросы на прерывание поступают от таймера и подаются на входы IRQ0, IRQ1 и IRQ2.

Для выбора нужной микросхемы при выполнении операций ввода-вывода используется дешифратор DD29, преобразующий два разряда адресной шины AB2 и AB3 в сигналы выбора CS. Сигналы выбора кристалла CS формируются только если один из сигналов IOR и IOW находится в активном состоянии. Необходимым условием выбора внешних по отношению к процессору устройств является равенство нулю младшего адресного разрядаAB0. Для хранения адреса в течение всего цикла шины используются регистры-защелки DD11 и DD12, управляемые сигналов ALE процессора. Шина данных умощняется за счет подключения шинных формирователей.

Память контроллера организована на четырех микросхемах; две из них образуют ПЗУ (DD2 и DD3) и две другие – ОЗУ (DD7 и DD8). Память выполнена в виде двух банков с целью передачи как двухбайтовых слов, так и отдельных байтов. Для выбора соответствующего банка используются сигнал BHE (разрешение старшего банка) и младший разряд адресной шины AB0. Разряд шины адреса AB14 служит для выбора ПЗУ или ОЗУ. Также в качестве управляющих сигналов, задающих направление передачи применяются MEMR и MEMW.

Шина управления состоит из четырех сигналов MEMR, MEMW, IOR, IOW, которые формируются на основе сигналов процессора RD, WR, M/IO.

В таблице 2.1 показано соответствие основных элементов структурной схемы контроллера используемым микросхемам.

Таблица 2.1 – Используемые микросхемы.

| Обозначение на схеме |

Микросхема |

| DD1 |

К1810 ГФ84 |

| DD2, DD3 |

К556 РТ16 |

| DD6 |

К1810 ВМ86 |

| DD7, DD8 |

К537 РУ17 |

| DD11, DD12 |

К1810 ИР82 |

| DD13, DD14 |

К1810 ВА86 |

| DD15, DD16 |

К580 ВВ55 |

| DD17 |

К1810 ВИ54 |

| DD18 |

К1810 ВН59А |

| DD27 |

К155 ТМ2 |

| DD28 |

К155 ИР1 |

| DD29 |

К155 ИД3 |

РАЗРАБОТКА РАБОЧЕЙ ПРОГРАММЫ КОНТРОЛЛЕРА

Структура данных

В данном проекте фоновым процессом является передача данных. В связи с этим опишем используемые переменные и структуры.

К основной структуре можно отнести два массива. Один из них служит буфером приемника и занимает в памяти ячейки с 0000 по 2FFFh. Указателем в этом массиве служит переменная RecCount. Второй массив SendBuf является буфером передатчика. За его заполнением следит отдельная задача, не рассматриваемая в данном проекте. При заполнении этого буфера данными флаг BufReady устанавливается в единичное состояние. Буфер SendBuf имеет размер 255 байт и располагается с адреса 3000h по адрес 30FFh. Указателем на очередной элемент буфера служит переменная SendCount. В таблице 3.1 описаны используемые переменные.

Таблица 3.1 – Описание используемых переменных

| Переменная |

Размер |

Расположение |

Описание |

| TimeVar |

3 байта |

3100h |

Переменная хранит время в секундах с начала работы контроллера |

| BufReady |

1 байт |

3104h |

Флаг готовности буфера передатчика |

| RecCount |

2 байта |

3106h |

Указатель буфера приемника |

| SendCount |

2 байта |

3108h |

Указатель буфера передатчика |

| Sentry |

1 байт |

310Ah |

Переменная – точка входа в процедуру передатчика |

| FS |

1 байт |

310Ch |

Флаг работы процедуры передатчика (анализируется “службой времени”) |

Переменная TimeVar обслуживается счетчиком времени. Ее значение периодически используется для процедурой формирования очередного сообщения.

Переменная Sentry необходима для работы однопроходной формы задачи. В ней хранится метка входа в процедуру.

Переменная FS является сигнализатором того, что процесс передачи в данный момент активен. В случае “зависания” по этим флагам служба времени определяет конфликтную задачу и отображает ее номер на индикаторе.

Счетчик байтов SendCount в процессе передачи сообщения изменяет свое значение от 0 до FF.

Схемы алгоритмов процессов в автономной форме

Схема алгоритма процесса самодиагностики в автономной форме показана на рисунке 3.1.

Рисунок 3.1 – Автономная форма алгоритма процесса самодиагностики.

Процесс самодиагностики инициируется по прерываниям от таймера. Заключается в подсчете контрольной суммы ПЗУ и сравнении ее с известным значением. При несовпадении индикатор готовности гасится и процессор останавливается (вводится в бесконечный цикл)

Схема алгоритма процесса приема в автономной форме показана на рисунке 3.2.

Рисунок 3.2 – Автономная форма алгоритма процесса приема.

На рисунках 3.3 и 3.4 более подробно раскрыт состав блоков “прием символа” и “передача символа”.

Рисунок 3.3 – Состав блока “прием символа”.

Рисунок 3.4 – Состав блока “передача символа”.

Алгоритм приема информации реализует прием пакетов в формате X-Modem.

Контроль получаемых сообщений реализуется с помощью подсчета контрольной суммы.

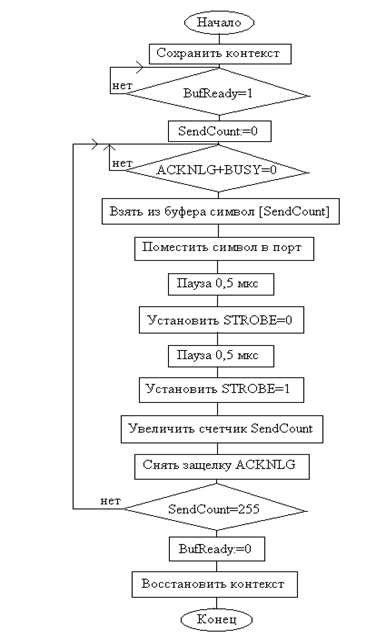

На рисунке 3.5 показана схема алгоритма передачи информации. Передатчик начинает работать, если буфер данных заполнен символами. Об этом сигнализирует флаг BufReady. После окончания передачи программа должна снять этот флаг – это служит запросом для процедуры подготовки данных.

Рисунок 3.5 – Автономная форма алгоритма процесса передачи.

Передача осуществляется порциями по 256 байт. Первые три байта – текущее время в секундах от начала работы контроллера.

Задача “службы времени” разбита на две части: Одна из них следит за текущим временем и формирует переменную, содержащую значение времени с момента включения контроллера, а другая часть контролирует отсутствие “зависаний” выполняемых задач.

На рисунке 3.6 показаны схемы алгоритмов для обеих частей задачи.

Рисунок 3.6 – Автономная форма алгоритмов процессов “службы времени”.

Схемы алгоритмов рабочей программы. Фоновый процесс

В графической части представлена схема алгоритма процесса передачи в однопроходной форме. После размыкания циклов задачи получилось две ветви. Первая – ожидание заполнения буфера данных. Вторая – собственно посылка буфера. За один проход задачи посылается один символ. Выбор ветви осуществляется с помощью переменной Sentry. Обмен информацией идет по стандарту интерфейса ИРПР-М.При посылке байта для соблюдения необходимых временных интервалов формируются паузы не менее 0,5 мкс. При проверке готовности приемника происходит логическое сложение сигналов BUSY и ACKNLG, и если результат равен нулю, выполняется отправка одного байта. По окончании передачи всего сообщения флаг готовности буфера сбрасывается.

3.4 Схемы алгоритмов рабочей программы. Подпрограмма обработки прерываний

Подпрограмма самодиагностики запускается по прерыванию от таймера. В однопроходном варианте присутствует три ветви. Первая ветвь пустая. Она выполняется диспетчером, если не возникало прерывания от таймера. Вторая ветвь служит для инициализации счетчика контрольной суммы. Обнуляется переменная – указатель и переменная, запоминающая текущее значение КС. В третьей ветви выполняются действия по суммированию содержимого ПЗУ. При достижении конечного адреса происходит сравнение полученного значения контрольной суммы с проверочным. При совпадении процедура устанавливает точку входа на первую ветвь, включает индикатор готовности и заканчивает работу. При ошибке КС индикатор готовности гасится и процессор зацикливается.

Текст фрагмента рабочей программы

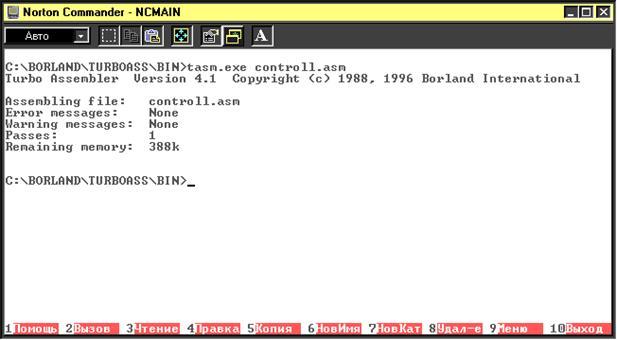

Фрагмент программы, представленный в приложении полностью соответствует описанной выше схеме алгоритма. Программа выполнена в виде самостоятельного модуля. Трансляция проводилась с помощью ассемблера TASM 5.0. Результаты работы транслятора показаны на рисунке 3.7.

Рисунок 3.7 – Результаты работы транслятора

Программа состоит из четырех основных частей. В первой части происходит сохранение используемых регистров и опрос переменной, хранящей точку входа в основное тело программы. При этом происходит выбор одной из ветвей прохода задачи. Вторая часть реализует первую ветвь алгоритма и начинается сметки Е0. Здесь осуществляется проверка готовности буфера и, при необходимости, изменение точки входа. Третья часть программы реализует вторую ветвь алгоритма. Если приемник готов, то выполняется посылка одного байта и изменение счетчика символов. И, наконец, четвертая часть программы (метка EXLABEL) завершает проход задачи, восстанавливает регистры и передает управление вызвавшей программе.

|