| Федеральное агентство по образованию

Государственное образовательное учреждение

высшего профессионального образования

Дальневосточный государственный технический университет

(ДВПИ им. В.В. Куйбышева)

Кафедра конструирования и производства радиоаппаратуры

Реферат

на тему:

«Микропроцессорный комплект серии К580»

2010

Содержание

1. Организация центрального процессора

2. Подключение памяти

3. Подключение интерфейсных программируемых БИС

4. Программная модель микропроцессорной системы

5. Методы адресации и примеры команд

6. Программирование на языке ассемблера

7. Программирование БИС параллельного интерфейса

8. Программирование таймера и контроллера прерываний

1. Организация центрального процессора

Микропроцессор серии К580 имеет 8-разрядную шину данных и 16-разрядную шину адреса. Шина адреса обеспечивает адресацию памяти объемом до 64 Кбайт и 256 портов ввода/вывода. Нагрузочная способность выходов МП невелика (один ТТЛ - вход), поэтому при построении системной магистрали их нужно буферировать. МП имеет средства обслуживания запросов прерывания, средства управления в режимах ожидания и прямого доступа к памяти (режим захвата).

Для построения центрального процессора на основе БИС К580ВМ80А (рисунок 1) дополнительно требуются микросхемы формирования сигналов синхронизации (тактовый генератор К580ГФ24) и сопряжения с системной магистралью (системный контроллер К580ВК28 и два шинных формирователя К580ВА86).

Тактовый генератор вырабатывает не перекрывающиеся положительные импульсы F1 и F2 амплитудой 12 В (для работы МП требуется три источника питания: +12 В, +5 В, -5 В). При частоте тактовых импульсов 2 МГц выбирается кварцевый резонатор на 18 МГц. Время, необходимое для извлечения одного байта из памяти или устройств ввода/вывода, или для выполнения простейших команд, называется машинным циклом. В общем случае время выполнения команды составляет 1-5 машинных циклов (М), каждый из которых включает 3-5 машинных тактов (Т). Во втором такте Т2 каждого машинного цикла на шину данных МП выдается байт состояния (см. рисунок 2), который по сигналу SYNC фиксируется в системном контроллере SC и используется для формирования сигналов обращения к памяти (MEMR, MEMW) и устройствам ввода/вывода (IOR, IOW). Системный контроллер выполняет также роль буфера шины данных и формирует сигнал подтверждения прерываний INTA.

|

|

Машинный цикл 1

|

Машинный цикл 2

|

|

|

Такт 1

|

Tакт 2

|

Tакт 3

|

Tакт 4

|

Tакт 1

|

Tакт 2

|

Tакт 3

|

| F1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| F2

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SYNC

|

|

|

|

|

|

Рисунок 2 – Диаграммы синхронизации процессора на базе К580ВМ80А.

Буфер шины адреса реализован с помощью 8-разрядных шинных формирователей К580ВА86. При логической единице на входе ОЕ (режим захвата системной магистрали контроллером ПДП) шина адреса МП переходит в состояние разомкнутого выхода.

Работа по программе является основным режимом работы МП. После системного сброса (при включении источника питания он происходит автоматически за счет RC-цепи, подключенной к входу RESIN тактового генератора) в программном счетчике устанавливается адрес нулевой ячейки памяти. Процессор считывает байт информации из этой ячейки и расшифровывает его как код операции первой команды. Если команда двух- или трехбайтовая, то в последующих циклах выбираются недостающие один или два байта из следующих ячеек памяти. Процессор выполняет первую команду, а программный счетчик формирует адрес следующей команды, увеличивая свое содержимое после каждого чтения из памяти. Команды, расположенные в последовательных ячейках памяти, выполняются до тех пор, пока не встретится команда перехода, скачком изменяющая содержимое программного счетчика.

В процессе выполнения программы МП может перейти в режим ожидания (WAIT=1), если нет сигнала готовности внешних устройств RDIN. При появлении этого сигнала работа возобновляется

Если разрешены прерывания, то по сигналу запроса INT от внешнего источника работа по программе прерывается для выполнения специальной подпрограммы обслуживания прерывания. Последней командой этой подпрограммы обычно предписывается возврат к выполнению основной программы.

По сигналу HLD (запрос ПДП) центральный процессор отключается от шин адреса и данных: буфера этих шин переходят в высокоимпедансное состояние.

2. Подключение памяти

Рассмотрим вариант подключения к системной магистрали устройств памяти с использованием микросхем перепрограммируемых ПЗУ с ультрафиолетовым стиранием типа К573РФ5 и ОЗУ статического типа К537РУ9 (рис.3). Каждая из микросхем образует страницу памяти объемом 2 Кбайта, выбор нужного слова из которой производится с помощью адресных сигналов А0-А10. Выбор нужной страницы осуществляет дешифратор К555ИД7 по состоянию старших разрядов адресной шины A11-A15. В данном примере ячейки ПЗУ и ОЗУ занимают в адресном пространстве МП соответственно области 0000H-07FFH и 0800H-0FFFH.

Подключение выходов микросхем памяти к шине данных производится при подаче логического нуля на входы разрешения выхода ОЕ (сигнал MEMR). Направление передачи информации в ОЗУ изменяется в зависимости от сигнала на линии MEMW шины управления. При необходимости можно включить еще шесть страниц ОЗУ или ПЗУ. Для этого потребуется еще шесть микросхем выбранного типа.

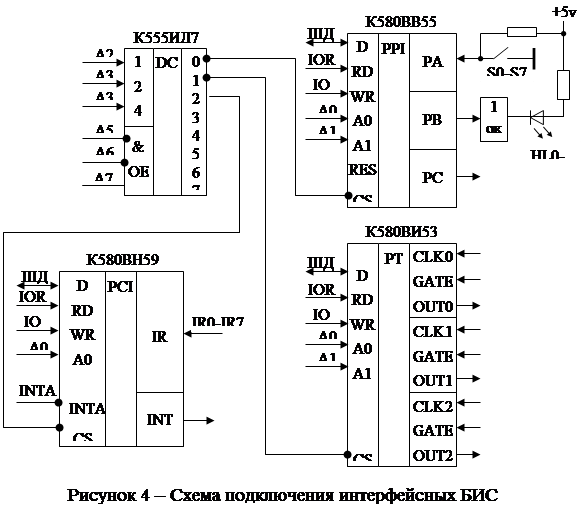

3. Подключение интерфейсных программируемых БИС

Рассмотрим подключение к системной магистрали БИС параллельного интерфейса K580BB55, программируемого таймера К580ВИ53 и контроллера прерываний К580ВН59 (рис.4).

Параллельный интерфейс (PPI) позволяет переключать шину данных МП на работу с одним их трех портов ввода/вывода: PA, PB, PC. После системного сброса все три порта настроены на режим ввода информации. При необходимости можно изменить режим работы каждого из портов. Для этого через шину данных МП в регистр управляющего слова PPI (РУС1) программно заносится управляющая информация. Адресация к конкретному порту производится с помощью адресных сигналов АО и А1. При этом сочетаниям A1, А0 вида 00,01,10, 11 соответствуют порты РА, РВ, PC и РУС1. Дешифрация старших разрядов адреса портов ввода/вывода осуществляется дешифратором К555ИД7. Нетрудно установить (см. рис.4), что портам параллельного интерфейса присвоены адреса 80Н, 81Н, 82Н и 83Н. В рассматриваемом примере порт РА используется для ввода информации в МП с восьми датчиков (имитируются линейкой тумблеров S0-S7), порт РВ - для вывода информации на линейку светодиодов HL0-HL7.

Программируемый таймер (РТ) содержит три 16-разрядных счетчика, работающих па вычитание. Счетчики могут быть запрограммированы для работы в одном из шести режимов при двоичном либо двоично-десятичном счете. Каждый из счетчиков имеет тактовый вход CLK, вход разрешения счета GATE и выход OUT (на рисунке выходы счетчиков не показаны). Командами ввода и вывода можно осуществить начальную загрузку счетчиков и считывание их состояний в МП.

Адресация трех счетчиков и управляющего регистра таймера производится с помощью двух адресных входов АО и А1 и входа CS. Можно установить (см. рис.4), что портам таймера соответствуют адреса 84Н (СТ0), 85Н (СТ1), 86Н (СТ2) и 87Н (РУС2).

Контроллер прерываний (PCI) реализует до восьми уровней запросов на прерывание (векторная система) с возможностью программного маскирования и изменения приоритета. Принимая запросы на прерывания от внешних устройств IR0-IR7 (это могут быть, в частности, сигналы, формируемые таймером или параллельным интерфейсом), контроллер формирует сигнал INT для микропроцессора от того канала, который в данный момент имеет наивысший приоритет. От МП контроллер получает сигнал подтверждения прерывания INTA. Управляющие регистры контроллера прерываний имеют адреса 88Н и 89H.

При обращении к портам ввода/вывода, для адресации которых достаточно одного байта адресного кода, процессор дублирует в старшем байте шины адреса содержимое младшего байта.

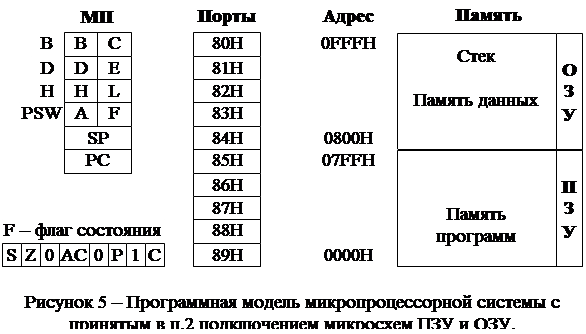

4. Программная модель микропроцессорной системы

С точки зрения программиста микропроцессор К580ВМ80А имеет следующие доступные ресурсы (рис.5):

1) 8-битовый аккумулятор А и шесть 8-разрядных регистров общего назначения (РОН) В, С, D, E, H, L;

2) 8-битовый регистр признаков F, в котором сохраняются пять признаков результата выполнения арифметических и логических операций в МП (бит знака S, бит нуля Z, бит четности Р, бит переноса С. бит дополнительного переноса АС);

3) 16-разрядный программный счетчик (счетчик команд) “program counter” PC, в котором хранится адрес следующей команды;

4) 16-разрядный указатель стека “stek point” SP, хранящий адрес ячейки памяти, куда был записан последний введенный в стек байт.

Ряд команд МП манипулирует регистровыми парами B, D, H, PSW (слово состояния программы). Пара регистров обычно содержит либо адрес ячейки памяти, либо два байта непосредственных данных.

В начальной области памяти (обычно в ПЗУ) располагается программа пользователя. Затем (обязательно в ОЗУ) идет память данных и стек. Стек - специально организованная область ОЗУ, предназначенная для временного хранения данных или адресов. Число, записанное в стек последним, извлекается из него первым. Указатель стека SP хранит адрес последней ячейки стека, в которой записана информация. При вызове подпрограммы в стеке автоматически сохраняется адрес возврата в основную программу. Как правило, в начале каждой подпрограммы сохраняют в стеке содержимое всех задействованных при ее выполнении регистров, а в конце подпрограммы восстанавливают их из стека.

5. Методы адресации и примеры команд

Система команд микропроцессора содержит 78 базовых команд (общее число команд с учетом возможных модификаций - 244): пересылки данных, обработки данных и управления ходом выполнения программы.

Программа может непосредственно составляться в виде последовательности машинных двоичных кодов команд, для более компактной формы которых используется их шестнадцатиричное представление. Более удобно пользоваться мнемоническими обозначениями команд, т.е. писать ее на языке ассемблера. Специальная программа Ассемблер может перевести с помощью ЭВМ рабочую программу МП в машинные коды. Но и при ручной трансляции (она может потребоваться при выполнении лабораторных работ на отладочных устройствах) предварительная запись программы на мнемоническом языке более наглядна.

Система команд микропроцессора i8080 использует различные методы адресации данных:

прямая адресация (адрес порта указывается во втором байте команды ввода данных в регистр аккумулятор IN

)

IN PA

; (A) ¬ (PA) DBH  КОП – код операции IN

КОП – код операции IN

80H  2-байт – адрес порта PA 2-байт – адрес порта PA

регистровая прямая адресация (в команде задается код пары РОН, где находится операнд данных)

INX

H

; (HL) ¬ (HL)+1 23H  КОП – код операции INX

КОП – код операции INX

регистровая косвенная адресация (адрес ячейки памяти, где находится операнд, определяется содержимым пары РОН)

ADD

M

;

(A) ¬ (A)+((HL)) 86H  КОП – код операции ADD

КОП – код операции ADD

непосредственная адресация (операнд содержится в команде: младший байт – во втором, старший байт – в третьем байтах команды)

LXI

H

, 850

H

;

(HL) ¬ 850H 21H  КОП – код операции LXI

КОП – код операции LXI

50H  2-й байт 2-й байт

80H  3-й байт 3-й байт

стековая адресация (адрес ячейки памяти, содержащей операнд, находится в указателе стека SP)

PUSH PSW;

((SP)-1) ¬ (A), ((SP-2) ¬ (F), (SP) ¬ (SP)-2

F5H  КОП – код операции записи в стек служебного слова. КОП – код операции записи в стек служебного слова.

6. Программирование на языке ассемблера

Язык ассемблера допускает представление всех элементов программы в символической (буквенно-цифровой) форме, отражающей их содержательный смысл. В качестве алфавита допустимых символов принят код ASCII (американский стандартный код для обмена информацией). Каждая строка ассемблера соответствует одной команде или псевдокоманде (директиве) и может содержать поля метки, мнемоники команды, операнда и комментария. При наличии в программе синтаксических ошибок ассемблер в процессе трансляции выдает сообщения об ошибках.

Метка ассоциируется с 16-битовым адресом той ячейки памяти, где будет размещен первый байт отмеченной команды. Использование меток освобождает программиста от необходимости оперировать абсолютными адресами памяти при записи команд передачи управления. Метка должна начинаться с буквы и заканчиваться двоеточием, может содержать до шести символов. Не допускается использовать в качестве меток ключевые слова (мнемоники команд и директив). Символическое обозначение должно быть уникальным (может появиться в поле метки только один раз).

Мнемокод команды может включать до четырех символов и вместе с обозначениями операндов образует группу ключевых слов ассемблера.

Поле операнда содержит числовые и символьные непосредственные данные, обозначения регистров и регистровых пар МП, адреса памяти. Возможно использование выражений, содержащих простейшие арифметические и логические операции, обработку которых ассемблер при трансляции производит в формате 16-разрядных двоичных чисел. Операнд в виде строки символов, заключенной в апострофы, транслируется в последовательность кодов ASCII этих символов.

Поле комментария начинается с точки с запятой и полностью игнорируется ассемблером. В поле комментария фиксируется обычно функция, которую выполняет группа команд в конкретной прикладной программе.

Кроме команд программа может содержать директивы ассемблера:

ORG

– начальный адрес массива, END – прекращение трансляции, EQU – эквивалентность (присвоение), DB – определить байт и тд.

Команды микропроцессора серии К580 (

i

8080)

| Команда

|

N

б

|

N

т

|

Описание команды

|

Флаги

|

| Группа команд пересылки данных

|

| MOV r1,r2

|

1

|

5

|

Пересылка данных из r2 в r1

|

|

| MOV М,r

|

1

|

7

|

Пересылка данных из r в память

|

|

| MOV r,М

|

1

|

7

|

Пересылка данных из памяти в r

|

|

| XCHG

|

1

|

4

|

Обмен данными между парами регистров HL и DL

|

|

| MVI r,d8

|

2

|

7

|

Занесение байта данных в регистр

|

|

| MVI M,d8

|

2

|

10

|

Занесение байта данных в память

|

|

| LXI rp,d16

|

3

|

10

|

Занесение двух байтов данных в пару регистров ( B,D,H,SP )

|

|

| LDAX rp

|

1

|

7

|

Занесение в А содержимого ячейки, косвенно адресуемой парой регистров (B или D)

|

|

| LDA adr16

|

3

|

13

|

Загрузка в А содержимого ячейки с указанным адресом

|

|

| STAX rp

|

1

|

7

|

Занесение содержимого А в ячейку, косвенно адресуемую парой регистров (B или D)

|

|

| STA adr16

|

3

|

13

|

Занесение содержимого А в ячейку с указанным адресом

|

|

| LHLD adr16

|

3

|

16

|

Загрузка в регистры H, L содержимого ячеек с указанным адресом и адресом, на единицу большим

|

|

| SHLD adr16

|

3

|

16

|

Занесение содержимого регистров H,L в две ячейки памяти

|

|

| Группа команд обработки данных

|

| ADD r

|

1

|

4

|

Сложение содержимого r и А

|

Z,S,P,C,AC

|

| ADD M

|

1

|

7

|

Сложение содержимого ячейки памяти и А

|

Z,S,P,C,AC

|

| ADС r

|

1

|

4

|

Сложение содержимого r и А с учетом переноса С

|

Z,S,P,C,AC

|

| ADС M

|

1

|

7

|

Сложение содержимого ячейки памяти и А с учетом переноса С

|

Z,S,P,C,AC

|

| DAA

|

1

|

4

|

Десятичная коррекция А

|

Z,S,P,C,AC

|

| Команда

|

N

б

|

N

т

|

Описание команды

|

Флаги

|

| SUB r

|

1

|

4

|

Вычитание содержимого r из A

|

Z,S,P,C,AC

|

| SUB M

|

1

|

7

|

Вычитание содержимого ячейки памяти из A

|

Z,S,P,C,AC

|

| SBB r

|

1

|

4

|

Вычитание содержимого r из A с заемом

|

Z,S,P,C,AC

|

| SUBB M

|

1

|

7

|

Вычитание содержимого ячейки памяти из A с заемом

|

Z,S,P,C,AC

|

| ANA r

|

1

|

4

|

Поразрядное «И» над содержимым r и A

|

Z,S,P,C=0,

AC=0

|

| ANA M

|

1

|

7

|

Поразрядное «И» над содержимым ячейки памяти и A

|

Z,S,P,C=0,

AC=0

|

| XRA r

|

1

|

4

|

Поразрядное «Исключающее ИЛИ» над содержимым r и A

|

Z,S,P,C=0,

AC=0

|

| XRA M

|

1

|

7

|

Поразрядное «Исключающее ИЛИ» над содержимым ячейки памяти и A

|

Z,S,P,C=0,

AC=0

|

| ORA r

|

1

|

4

|

Поразрядное «ИЛИ» над содержимым r и A

|

Z,S,P,C=0,

AC=0

|

| ORA M

|

1

|

7

|

Поразрядное «ИЛИ» над содержимым ячейки памяти и A

|

Z,S,P,C=0,

AC=0

|

| CMP r

|

1

|

4

|

Сравнение содержимого r и A

|

Z,S,P,C,AC

|

| CMP M

|

1

|

7

|

Сравнение содержимого ячейки памяти и A

|

Z,S,P,C,AC

|

| ADI d8

|

2

|

7

|

Сложение байта и A

|

Z,S,P,C,AC

|

| ACI d8

|

2

|

7

|

Сложение байта и A с учетом переноса

|

Z,S,P,C,AC

|

| SUI d8

|

2

|

7

|

Вычитание байта из A

|

Z,S,P,C,AC

|

| SBI d8

|

2

|

7

|

Вычитание байта из A с учетом переноса

|

Z,S,P,C,AC

|

| ANI d8

|

2

|

7

|

Поразрядное «И» байта и A

|

Z,S,P,C=0,

AC=0

|

| XRI d8

|

2

|

7

|

Поразрядное «исключающее ИЛИ» байта и A

|

Z,S,P,C=0,

AC=0

|

| Команда

|

N

б

|

N

т

|

Описание команды

|

Флаги

|

| ORI d8

|

2

|

7

|

Поразрядное «ИЛИ» байта и A

|

Z,S,P,C=0,

AC=0

|

| CPI d8

|

2

|

7

|

Сравнение содержимого A и байта

|

Z,S,P,C,AC

|

| DAD rp

|

1

|

10

|

Сложение содержимого пары HL и регистровых пар (B,D,H,SP)

|

Z,S,P,C,AC

|

| INR r

|

1

|

5

|

Увеличение содержимого r на 1

|

Z,S,P,AC

|

| INR M

|

1

|

10

|

Увеличение содержимого ячейки памяти на 1

|

Z,S,P,AC

|

| DCR r

|

1

|

5

|

Уменьшение содержимого r на 1

|

Z,S,P,AC

|

| DCR M

|

1

|

10

|

Уменьшение содержимого ячейки памяти на 1

|

Z,S,P,AC

|

| INX rp

|

1

|

5

|

Увеличение содержимого пары регистров на 1

|

|

| DCX rp

|

1

|

5

|

Уменьшение содержимого пары регистров на 1

|

|

| RLC

|

1

|

4

|

Циклический сдвиг A влево

|

C

|

| RRC

|

1

|

4

|

Циклический сдвиг A вправо

|

C

|

| RAL

|

1

|

4

|

Циклический сдвиг A влево через перенос

|

C

|

| RAR

|

1

|

4

|

Циклический сдвиг A вправо через перенос

|

C

|

| CMA

|

1

|

4

|

Поразрядное инвертирование A

|

|

| STC

|

1

|

4

|

Установка признака переноса

|

C=1

|

| CMC

|

1

|

4

|

Инвертирование флага переноса

|

C=C C=C

|

| Группа команд управления ходом выполнения программы

|

| JMP adr16

|

3

|

10

|

Безусловный переход по адресу

|

|

| JC adr16

|

3

|

10

|

Переход по адресу при наличии переноса

|

|

| JNC adr16

|

3

|

10

|

Переход по адресу при отсутствии переноса

|

|

| JZ adr16

|

3

|

10

|

Переход по адресу при нуле

|

|

| JNZ adr16

|

3

|

10

|

Переход по адресу при отсутствии нуля

|

|

| JP adr16

|

3

|

10

|

Переход по адресу при плюсе

|

|

| Команда

|

N

б

|

N

т

|

Описание команды

|

Флаги

|

| JM adr16

|

3

|

10

|

Переход по адресу при минусе

|

|

| JPE adr16

|

3

|

10

|

Переход по адресу при четности

|

|

| JPO adr16

|

3

|

10

|

Переход по адресу при нечетности

|

|

| CALL adr16

|

3

|

17

|

Вызов подпрограммы

|

|

| CC adr16

|

3

|

11/17

|

Вызов подпрограммы при переносе

|

|

| CNC adr16

|

3

|

11/17

|

Вызов подпрограммы при отсутствии переноса

|

|

| CZ adr16

|

3

|

11/17

|

Вызов подпрограммы при нуле

|

|

| CNZ adr16

|

3

|

11/17

|

Вызов подпрограммы при отсутствии нуля

|

|

| CP adr16

|

3

|

11/17

|

Вызов подпрограммы при плюсе

|

|

| CM adr16

|

3

|

11/17

|

Вызов подпрограммы при минусе

|

|

| CPE adr16

|

3

|

11/17

|

Вызов подпрограммы при четности

|

|

| CPO adr16

|

3

|

11/17

|

Вызов подпрограммы при нечетности

|

|

| RET

|

1

|

10

|

Возврат

|

|

| RC

|

1

|

5/11

|

Возврат при переносе

|

|

| RNC

|

1

|

5/11

|

Возврат при отсутствии переноса

|

|

| RZ

|

1

|

5/11

|

Возврат при нуле

|

|

| RNZ

|

1

|

5/11

|

Возврат при отсутствии нуля

|

|

| RP

|

1

|

5/11

|

Возврат при плюсе

|

|

| RM

|

1

|

5/11

|

Возврат при минусе

|

|

| RPE

|

1

|

5/11

|

Возврат при четности

|

|

| RPO

|

1

|

5/11

|

Возврат при нечетности

|

|

| RST N

|

1

|

11

|

Повторный запуск с адреса 8N

|

|

| IN adr8

|

2

|

10

|

Ввод данных из порта в A

|

|

| OUT adr8

|

2

|

10

|

Вывод данных в порт из A

|

|

| PUSH rp

|

1

|

11

|

Занесение содержимого пары регистров (B,D,H,PSW) в стек

|

|

| POP rp

|

1

|

10

|

Выдача данных из стека в пару регистров (B,D,H,PSW)

|

Z,S,P,C,AC

|

| |

|

|

|

|

| Команда

|

N

б

|

N

т

|

Описание команды

|

Флаги

|

| XTHL

|

1

|

18

|

Обмен данными между вершиной стека и парой HL

|

|

| SPHL

|

1

|

5

|

Занести в указатель стека содержимое регистровой пары HL

|

|

| DI

|

1

|

4

|

Запретить прерывание

|

|

| EI

|

1

|

4

|

Разрешить прерывание

|

|

| NOP

|

1

|

4

|

Холостая операция

|

|

| HLT

|

1

|

7

|

Останов

|

|

Примечание:

Nб – число байт; Nт – число тактов;

В знаменателе дроби указано число тактов на выполнение операции при выполнении условия, в числителе – при невыполнении.

Рассмотрим примеры записи программ на языке ассемблера ASM80 (разработанного в соответствии с системой команд процессора i8080).

7. Программирование БИС параллельного интерфейса

При программировании БИС в регистр РУС1 командой OUT 83H записывается управляющее слово, которое определяет один из трех режимов работы портов параллельного интерфейса:

режим 0

-

программно управляемый ввод/вывод данных в синхронном режиме по трем 8-разрядным каналам РА, РВ и PC. Каждый канал может быть использован только для ввода или вывода информации, а канал PC дополнительно может быть разделен на два 4-разрядных канала;

режим 1

-

обмен данными с ВУ по каналам РА и РВ в асинхронном режиме и режиме прерывания программы. Управляющие сигналы при этом передаются по каналу PC;

режим 2

-

двунаправленный обмен данными с ВУ по каналу РА в режиме прерывания программы. Каналу РC придается пять линий канала PC для передачи и приема управляющих сигналов. Канал РВ может быть при этом запрограммирован на работу в режимах 0 или 1.

При программировании БИС используются два формата управляющего слова: первый предназначен для задания режимов работы и направления включения каналов, второй - для установки или сброса произвольного разряда канала PC. Признак формата содержится в старшем бите управляющего слова: 1 соответствует формату 1, а 0 -формату 2. В схеме, изображенной на рис.4, порты РА и РВ работают в режиме 0 и для программирования параллельного интерфейса нам понадобятся управляющие слова обоих форматов для режима 0.

Управляющее слово первого формата:

| D7

|

D6

|

D5

|

D4

|

D3

|

D2

|

D1

|

D0

|

| 1

|

0

|

0

|

PA

|

PC4-PC7

|

0

|

PB

|

PC0-PC3

|

Логическая «1» в соответствующем разряде настраивает обозначенный канал на ввод, логический «0» - на вывод информации. Порт С позволяет производить независимую настройку полупортов на ввод-вывод в режиме 0.

Управляющее слово второго формата:

| D7

|

D6

|

D5

|

D4

|

D3

|

D2

|

D1

|

D0

|

| 0

|

Х

|

Х

|

Х

|

D3

|

D2

|

D1

|

D0

|

В битах D6-D4 управляющего слова может быть произвольная информация.

8. Программирование таймера и контроллера прерываний

Контроллер прерываний (КП)

содержит регистры: запросов RGI

,

приоритетов RGB

,

обслуживания ISR

и масок прерывания RGM

. Запросы поступают на входы IR

0-

IR

7

и устанавливают соответствующие разряды регистра запросов RGI

. КП оценивает их приоритет и формирует запрос INT. Микропроцессор принимает INT, и если прерывания разрешены, то подтверждает прием выдачей флага INTA. КП устанавливает разряд ISR с наивысшим приоритетом, сбрасывает запрос в RGI и выдает на шину данных код команды CALL (0CDH). МП выдает еще два сигнала INTA, по которым КП выдает на ШД последовательно сначала младший, а затем старший байт адреса подпрограммы обслуживания прерываний.

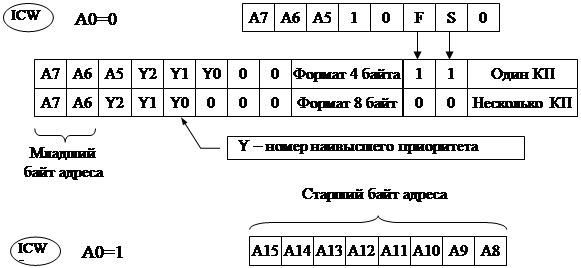

Установка КП в исходное состояние и настройка его на определенный режим работы по обслуживанию прерываний программируются двумя типами команд:

командами инициализации ICW1, ICW2;

командами управления режимом OCW1, OCW2, OCW3.

Команды ICW загружаются по команде OUT с учетом разряда АО. ICW1 используется при формировании младшего байта адреса подпрограммы, ICW2 задает старший байт адреса:

КП готов работать в режиме с фиксированными приоритетами запросов: IR0 - наивысший, IR7 - низший. Для задания других режимов в любой момент загружаются команды-приказы OCW (Operate Control Word):

Mi=1 – запрет прерывания по i-му каналу.

Сброс разряда регистра обслуживания ISR и циклический сдвиг приоритета. Записывается в подпрограмме обслуживания прерывания перед RET. Варианты приказа OCW2:

00100000 – сброс бита регистра обслуживания ISR с максимальным приоритетом;

10100000 - сброс бита ISR с максимальным приоритетом и назначение соответствующему входу низшего приоритета;

01100L2

L1

L0

– сброс бита ISR, определяемого полем L2

L1

L0

;

11000L2

L1

L0

- назначение входу L2

L1

L0

низшего приоритета.

Режим опроса, считывания состояния КП

В режиме опроса КП принимает запросы на прерывание от внешних устройств и формирует слово состояния опроса (D2-D0), содержащее номер запроса с наивысшим приоритетом. Обслуживание запроса происходит по требованию программы. Программно слово-состояние считывается (командой IN при А0=0), декодируется и осуществляется переход к соответствующей подпрограмме обслуживания прерываний.

Чтение регистра масок RGM осуществляется (командой IN при А0=1) без OCW3, регистра запроса RGI - после OCW3 с RIS=0. регистра обслуживания ISR - после OCW3 c RIS=1.

Формат F в ICW1 задает адресный интервал между начальными адресами подпрограмм обслуживания прерываний. Например, после выполнения команд

| Код операции

|

Комментарий

|

| EI

|

|

Разрешить прерывания

|

| MVI

|

A,36H

|

ICW1 – один КП, формат 4, A7A6A5=001

|

| OUT

|

88H

|

Адрес регистра управления КП при A0=0

|

| MVI

|

A,0

|

ICW2 (A15-A8=00000000)

|

| OUT

|

89H

|

Адрес регистра управления КП при A0=1

|

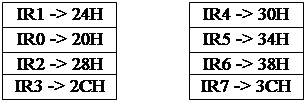

Начальные адреса подпрограмм обслуживания прерываний будут иметь следующие значения:

Программируемый интервальный таймер

. Режимы работы программируемого таймера поясняют временные диаграммы (рис.6), на которых показаны сигналы на выходе OUT счетчика (это может быть СТО, СТ1 или СТ2) в каждом режиме, если при программировании в него загружено число N=4.

| CLK

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Тактовые импульсы

|

| N = 4

|

| WR

|

|

|

Конец программирования

|

| |

|

| GATE

|

|

|

Аппаратное разрешение

|

| |

|

N·T

|

|

| Режим 0

|

|

Программная задержка

|

| |

|

|

|

| Режим 1

|

|

|

|

Ждущий мультивибратор

|

| |

|

|

|

N·T N·T

|

|

| Режим 2

|

|

|

|

|

|

|

|

|

Генератор такт. импульсов

|

| |

|

|

N·T N·T

|

|

| Режим 3

|

|

|

|

|

|

|

|

|

Генератор меандра

|

|

|

|

N·T N·T

|

|

| Режим 4

|

|

|

|

Программно-управл. строб

|

|

|

N·T N·T

|

|

| Режим 5

|

|

|

Аппаратно-управл. строб

|

Рисунок 6 – Диаграммы режимов работы программируемого таймера

Режим работы каждого счетчика задается записью в регистр управления таймера управляющего слова следующего формата (рис. 7):

Затем осуществляется загрузка каждого счетчика одним или двумя информационными байтами. Таймеры работают на вычитание. Микропроцессор может прочитать текущее значение числа Ni в любом счетчике таймера либо непосредственно с помощью команды IN, либо предварительно защелкнув его в буферном регистре счетчика путем ввода в регистр управления слова с D5=D4=0.

|