| Мікропроцесори.

1. Приклад організації циклічного виконання операцій.

Розрахувати цифровий пристрій, призначений для виконання операції множення двох 4-х розрядних слів. Множиме В=1101. Множник А=1011.

В 1101 множиме

А 1011 множник А 1011 множник

1101 частковий добуток 1

1101 частковий добуток 2 1101 частковий добуток 2

100111 частковий добуток 3

1101 частковий добуток 4 1101 частковий добуток 4

10001111 добуток

Мал. 1.

Як виплива з мал.1 операція множення полягає в послідовному виконанні двох простих операцій – знаходження суми двох слів і зсув вправо часткового добутку, або вліво множимого на один розряд. Звідси виплива, що для побудови пристрою, що виконуватиме вказану операцію, необхідно мати такі цифрові елементи:

- послідовний регістр;

- суматор;

- паралельні регістри для запам’ятовування даних;

- пристрій для управління.

На мал. 2 представлений можливий взаємозв’язок між елементами, які утворюють схему.

Множиме записується в регістр В з відкритими виходами, які підключаються до входів слова В у суматорі.

Множник А записується в старші розряди послідовного регістру, а виходи суматора підключаються до молодших розрядів.

Чотири молодші розряди виходу послідовного регістру з’єднані з входами слова В у суматорі.

Блок керування ( БК ) має два входи та два виходи.

Вхід синхронізації Т від зовнішнього тактового годинника організує частоту виконання операцій. Вхід D з виходу D7

старшого розряду послідовного регістру призначений для організації знаходження суми. Виходи БК V та С призначені відповідно для виконання операцій знаходження суми та операції зсуву інформації на 1 розряд в послідовному регістрі. Виконаня операції перемноження відбувається в наступній послідовності.

A A

V V

C C

D

T

Мал. 2.

При наявності першого сигналу Т повинна виконуватись операція знаходження суми В з інформацією, що записана в молодших розрядах послідовного регістру. На цей час там записаний нуль. При наявності сигналу “1” в D7

послідовного регістру в ПК формується команда V – потенційний сигнал, який дозволяє суматору SM виконати операцію і одночасно записати результат в молодші розряди послідовного регістру. При другому тактовому сигналі формується сигнал С, що зсуває інформацію послідовного регістру на 1 розряд і тим самим замінює в D7

значення останнього розряду множимого на передостанній. При наступному тактовому сигналі знов повинен формуватись сигнал V, але він може з’явитись лише у випадку, якщо в D7

на цей час знаходиться “1”. При наявності “0” в цьому розряді регістру сигнал V не з’являється і операція знаходження поточної суми не виконується. Далі знов формується сигнал С.

З аналізу роботи, не вдаючись в побудову графу станів та таблиці переходів, легко розрахувати схему ПК (мал. 3), робота якої зрозуміла без пояснень.

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

D | ПК |

| | V

| |

T | |

| |

| |

| | C

| |

| |

|_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ |

Мал. 3.

Робота розробленого кінцевого автомату може бути описана на алгоритмічному рівні (мал. 4), вона буде відповідати діаграмі станів.

Цей скорочений алгоритм повністю відповідає послідовності роботи схеми перемножувача, приведеного на мал. 2. Як схема, так і алгоритм не є повністю завершеними в тому плані, що вони не зв’язані з пристроями пам’яті, з яких можна брати нові дані для обробки та поміщати результат виконання операції. Якщо їх доповнити вказаними операціями, то наведений алгоритм буде завершений.

Кожна операція, що виконується в розглянутому алгоритмі і, відповідно, в схемі, називається мікрокомандою

.

Сформулюємо тепер початкову термінологію.

Завершений набір послідовності одиниць і нулів називається словом.

Слово, над яким виконуються якісь операції, називається операндом.

Слово, яке керує виконанням операцій з операндом називається командою.

Набір керуючих сигналів називається мікрокомаедою.

Завершена послідовність мікрокоманд, що закінчується виконанням операції називається мікропрограмою.

Принцип використання мікропрограм для реалізації алгоритмів називається мікропрограмуванням

. Мікропрограмування є одним з головних принципів, що лежать в основі більшості сучасних систем обробки інформації.

Приведена термінологія стосується алгоритма (мал.4). Відповідно ми маємо термінологію і до апаратних засобів, що реалізують алгоритм.

Регістр, в який заноситься операнд перед виконанням над ним операції називається регістром операнда.

Регістр, в який заноситься команда, під дією якої буде виконуватись операція називається регістром команд (РК).

Регістртр, в який заноситься результат виконання опрації називається регістром-акумулятором (РА).

В загальному вигляді арифметико-логічний пристрій (АЛП)

, в якому виконуються окремі мікрокоманди має вигляд, поданий на мал.5.

Запис. Зчит.

Запис. Запис.

Зчит. Зчит.

Мал.5

Розглянемо роботу ААП на прикладі виконання однієї операції. Спочатку по тактових сигналах “Запис” записується в РК код операції, а в РО – операнд. Але при подачі сигналу “Запис” в РО одночасно подається сигнал “Зчитування” з РА. Тому інформація, що зберігається в РА передається в частину РО. Після того, як процеси передачі інформації встановляться, подається сигнал, що забезпечує одночасне зчитування з РО і РК. Завдяки цьому на виходи комбінаційного АЛП одночасно поступають операнд і код операції. Одночасність забезпечується незалежно від того, в якому порядку подаються слова на входи регістрів. В цьому і полягає суть синхронізації. Через інтервал часу, достатній для встановлення процесів в АЛП, подається сигнал на запис результату в РА.

Розглянута схема дозволяє розкрити питання про те, як виконати найпростішу операцію, яка по відношенню до РА може розглядатись як заміна одного слова іншим. Більш повно суть виконання операцій пояснює схема, приведена на мал.6.

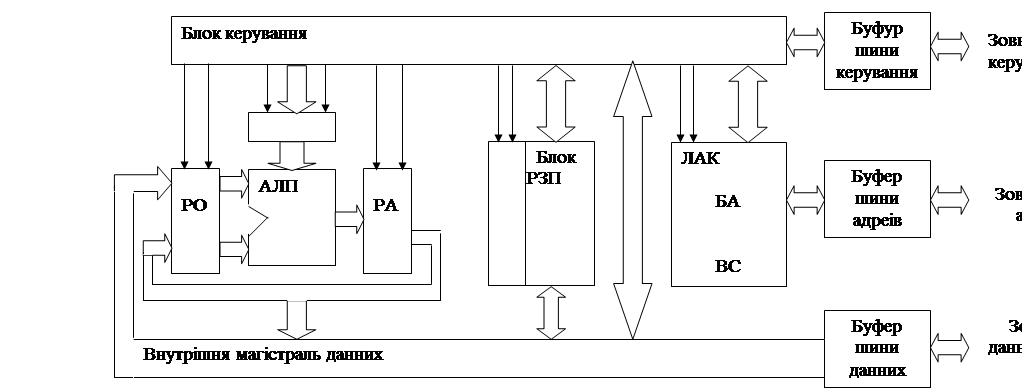

Блок регістрів загального призначення (РЗП) – це регістри, що призначені для тимчасового збереження інформації, що підлягає обробці. Головна особливість РЗП полягає в тому, що записати в ці регістри можливо тільки слова з внутрішньої магістралі данних. В цих регістрах зберігаються операнди, що підлягають обробці і сюди заносяться слова після виконання операцій.

Процедура виконання операцій зараз проходить в наступній послідовності. З БК поступають сигнали “Зчитування” на вибраний РЗП і сигнал “Запис” на РО. Необхідне слово проходить через внутрішню магісталь з вибраного РЗП в РО. Одночасно з БК поступає код операції на сигнал “Запис” на РК. Після виконання операції з БК поступає сигнал “Запис”, а потім сигнал “Зчитування” на РА і сигнал “Запис” на один з РЗП, куди поступає нове слово через внутрішню магістраль.

Але якщо необхідне слово відсутнє в РЗП, то його необхідно знайти в ОЗП за конкретною адресою. Формуванням адресів ОЗП займається спеціальний блок – блок адресації (БА).

Використовубться наступні способи формування адресів ОЗП.

Безпосередня адресація –

адрес елемента пам’яті або декількох адресів формується безпосередньо з БА.

Відносна адресація –

з БА виймається частина адресного слова і до нього додається (за правилами арифметики) друга його частина, яка може знаходитись, наприклад, в одному з РЗП.

Побічна адресація –

з БА вибирається адрес елемента ОЗП. Слово, що знаходиться по вибраному адресу використовується в якості адреси другого елемента ОЗП в якому і знаходиться необхідна інформація.

Складна адресація –

адрес елемента ОЗП, звідки виймається операнд, або куди розміщується результат, формується в результаті складних перетворень (асоціативна пам’ять). При виконанні окремих дій при відносній та складній адресації БА звертається до АЛП. При таких ситуаціях під дією БК між БА та АЛП проходить інтенсивний обмін інформацією.

З використанням добавлених блоків використання окремої операції проходить в наступній послідовності.

Етап 1.

Чергова команда з сформованої в БА адреса ОЗП через буфер шини данних подається на внутрішню магістраль данних. Буфер данних –

це регістр, що вирішує задачі синхронізації при обміні данними процесора з зовнішнім середовищем. Відповідні сигнали синхронізації для звернення до ОЗП формуються в БК. Одночасно сигнали синхронізації поступають в процесор по зовнішній шині керування і в БК перетворюються на необхідні внутрішні сигнали керування. Важливо пам’ятати, що описання внутрішньої мови МП може бути іншим, ніж мова використовуєма АЛП.

Етап 2.

Одна частина описання команди через внутрішю магістраль данних поступає в БК, який перетворює її в код операції та необхідний набір сигналів керування. Формування коду операції та керуючих сигналів – головна функція БК. Друга частина описання команди подається в БК, який перетворює її в адрес операнда.

Етап 3.

На основі сформованих на попередньому етапі адресів з пам’яті або, як виключення, з РЗП достається операнд, який по внутрішній магістралі данних подається на вхід АЛП. БК при цьому формує всі необхідні сигнали.

Етап 4.

АЛП виконує операцію в відповідності до раніше описаної послідовності.

Етап 5.

Результат операції через внутрішню магістраль данних подається в РЗП або через буфер данних в ОЗП по адресі, що формується в БА.

Етап 6.

БА формує адресу, по якій з БА виймається описання чергової команди.

Як відомо з опису роботи алгоритмів існують два можливі способи задання послідовності виконання правил алгоритма. Перший – це натуральна послідовність, відповідно до якої слідом за даним правилом виконується правило, безпосередньо слідуюче за ним. Стосовно до розглянутих схем це означає, що описання команд записується в елементи пам’яті послідовно по зростанню адреси елемента, тобто фізична адреса – це по суті номер елемента пам’яті.

Натуральна послідовність виконання команд реалізується за допомогою БА. Для цього в ньому знаходиться лічильник адресів команд (ЛАК), який вказує число, представляюче адресу команди, що виконується. Кожного разу після виконання команди це число підвищується на 1. Потім це число через буфер шини адресів передається в пам’ять для виводу чергової команди.

Другій спосіб задання послідовності виконання команд – це безумовний та умовний переходи. Безумовний перехід виконується на основі чергового правила алгоритма, тобто: слідом за даним словом виконується правило, команда (описання) якого зберігається в елементі пам’яті з такою адресою. Ця адреса входить до складу команди, або знаходиться по одному з вище описаних способів. В будь-якому випадку адреса чергової команди при реалізації правила безумовного переходу записується в ЛАК, замінюючи раніше існувавше там число. Всі ці дії виконуюються під керуванням БК.

Порядок виконання умовних переходів також задається черговим правилом алглритма. Також правило (команда) окрім адреси елемента пам’яті, що зберігає команду, до якої повинен виконуватись перехід, має описання деякої умови, наприклад a>b . Якщо ця умова виконується, адреса з команди умовного переходу записується в ЛАК, простіше, раніше записане число, що задавало адресу команди, збільшується на 1. Якщо ж умова не виконується, то перехід відбувається за правилами безумовного переходу. Перевірка виконання або невиконання умови виконується в АЛП, які помимо формування результату виконання операції видають спеціальні сигнали, наприклад “Результат=0”, “Результат має (-) знак”, які використовуються при прийнятті рішення і при виконанні умовного переходу.

Використовуються різні способи організації послідовності виконання команд, наприклад переривання. Перериванням

називається послідовність дій, в результаті яких виконання даного алгоритма тимчасово припиняється і замість цього починає виконуватись інший алгоритм. Щоб потім повернутись до виконання перерваного алгоритма, в перелік дій по реалізації переривань входять дії по перезапису числа лічильника ЛАК з РЗП в ОЗП. При багатосходинковому перериванні створюється послідовність чисел ЛАК і РЗП, що зберігаються в ОЗП в заданому порядку. Цей порядок забезпечується спеціальним пристроєм – показником стеку (ПС), який також входить до складу БА.

Переривання виконуються по “Запросу на переривання”, що надходить зовні по шині керування.

Шина керування є не настільки розгалудженою, як адресна. По ній, крім сигналів переривання, проходять сигнали синхронізації, готовності підключених зовні пристроїв та ін.

З викладеного виплива важливий висновок: яка б не була операція, що виконується процесором, вона вимагає для реалізації великої кількості сигналів керування. Всі ці сигнали умовно розподіляються на такі групи:

- код операції;

- адресна частина;

- ознаки;

і в цілому формують формат команди.

Прийнято розподіляти різні операції на п’ять основних груп.

Операції пересилки.

Вони передбачають перезапис слова або групи слів з одного елемента пам’яті в інший. Типовим прикладом таких операцій є перезапис слів з ОЗП в РЗП та навпаки. АЛП у виконанні таких операцій участі не бере. БК виробляє сигнали, що відкривають входи-виходи відповідних регістрів, або елементів пам’яті. Звідки взяти пересилаєме слово і куди його помістити визначають керуючі сигнали, які об’єднані в адресній частині (більш детально ці питання будуть розглянуті пізніше). В найбільш простих випадках пересилки слова з одного РЗП в інший, адресна частина має всього два сигнали, один з яких дозволяє зчитування з РЗП відправника, а інший – дозвіл запису в РЗП одержувача. Пересилка відбувається через внутрішню магістраль даних. У випадках складних видів адресації адресна частина може складатись з декількох слів, які є або адресами, або числами, що додаються до адреси. Пересилка в таких випадках може виконуватись на протязі декількох етапів, а в формуванні адресів активну участь бере АЛП, який одержує відповідні команди від БК.

Арифметико-логічні операції

. Ці операції виконуються АЛП. Особливість виконання таких операцій вже була описана вище. Адресна частина включає адресу операнда і може складатись з одного біта, дозволяючого читати з РЗП, або групи слів, які беруть участь у формуванні складної адреси.

Операції переходів по програмі.

В даному випадку код операції відноситься до блоку адресації. АЛП використовується лише коли перевіряється виконання умовного переходу. Адресна частина зберігає адресу елемента пам’яті, з якої дістається команда, що повинна виконуватись слідом за даною. Умови переходу можуть знаходитися в коді операції, а також в тій частині команди, що називається словом “ознаки”.

Операції звернення до зовнішних пристроїв.

Особливості цих операцій будуть розглянуті пізніше. Формально їх виконання майже не відрізняється від операцій пересилки.

Решта операцій.

До цієї групи відносяться операції, які не ввійшли до попередніх груп, наприклад, операції переривання.

Викладений в цьому розділі матеріал дає загальні поняття про принцип побудови процесора та деякі особливості взаємодії його блоків. Реальні процедури відрізняються за різними ознаками, але завжди залишаються наступні базові принципи їх побудови:

1. Процесор реалізує алгоритм, описання якого зберігається в тому чи іншому пристрої пам’яті, зовнішньому по відношенню до процесора (говорять, процесор працює по зберігаємій програмі).

2. Принцип мікропрограмування – кожна операція управляється відповідною мікрокомандою. Це найважливіший принцип, що забезпечує універсальність процесора.

3. Наявність системи внутрішньої та зовнішньої синхронізації.

4. Принцип магістральної організації.

Загальна структура мікропроцесорної системи.

Інтерфейс.

Виконання того чи іншого алгоритма можливо при наявності мікропроцесора та пристроїв, в яких зберігається програма. Відомо, що програма – це сукупність команд (правил), що виконуються в послідовності, заданій алгоритмом. Команди вибираються з пам’яті в послідовності, що задається процесором. Процесор визначає адреси елементів пам’яті, в яких зберігаються необхідні данні. Данні передаються в процесор, де перетворюються у відповідності з командами, і результати операції передаються знову в пам’ять.

Вказана взаємодія процесора з зовнішньою пам’яттю відображається мал.7.

Вказана взаємодія процесора з зовнішньою пам’яттю відображається мал.7. Мал. 7.

Будь-яка мікропроцесорна система працює разом з рядом зовнішних пристроїв, одержуючи від них необхідну інформацію та передаючи іншу. Для зв’язку з зовнішними пристроями існує інтерфейс (interface). Цим терміном позначається весь комплекс пристроїв, правил та технічних засобів, що регламентують та забезпечують обмін інформацією між мікропроцесором (включаючи пам’ять) та зовнішними пристроями. Головними в інтерфейсі є шини, або, як їх часто називають, магістралі. Магістраль – це сукупність провідників, для яких строго нормовані рівні “0” та “1”. Потужність сигналів на шинах повинна бути достатньою для живлення необхідної кількості приєднуємих до них пристроїв. Для забезпечення цієї потужності використовуються спеціальні мікросхеми - шинні підсилювачі (ШП). Реальні мікросхеми ШП забезпечують рівні сигналів ТТЛ, мають вихідну потужність 500 мВт, та струм навантаження до 100 мА. Коефіцієнт підсилення їх – 105.

ШП повинні підсилювати сигнал, що передається в двох напрямках.

Варіант ШП наводиться на мал. 8.

Вх Вих Вх Вих у VT5 у Вх Вих Вх Вих у VT5 у Мал. 8. а) б)

Підсилювач ключового типу виготовлений з двох каскадів на VT1, VT2 та VT3,VT4 відповідно, та однонаправленого ключа на VT5. Двохкаскадний підсилювач підсилює вхідні сигнали без інверсії, а передача сигнала на вихід забезпечується при наявності нульового керуючого сигналу у

. При у=1 транзистор VT5 закривається і канал “Вх”, “Вих” обривається.

В ШП використовується два типи підсюлювачів. Другий тип передає сигнал при у=1, а при у=0 закривається. Реальна схема ШП містить в собі ряд ШП (на 4, 8 інформаційних каналів) (мал. 9).

Схема допоміжно забезпечується спеціальною логікою, яка вирішує проблеми однонаправленої передачі інформації, відповідно до табл.1. Допоміжна логіка обумовлена необхідністю гарантії тільки однонаправленої передачі інформації. При проектуванні складних цифрових схем виходять з того, що розроблена схема повинна бути такою, щоб була виключена будь-яка комбінація сигналів, при якій можлива поява аварійної ситуації.

Одною з можливих аварійних ситуацій в даному випадку є можливість одночасного включення двох підсилювачів, що призведе до збудження неконтрольованих автоколивань в них.

За призначенням, шини поділяються на три типи:

- адресні;

- данних;

- керування.

Але реально як в мікропроцесорній техниці, так і в комп’ютерній часто дві шини суміщують шляхом мультіплексування, що дещо знижує їх швидкодію, але набагато зменшує кількість виводів мікросхем.

Х2 Х2 |

Х1

|

У1

|

У2

|

А0

® В0

|

В0

® А0

|

|          0 0

0

1

1

|

0

1

0

1

|

0

1

1

1

|

0

0

0

1

|

0

0

0

1

|

1

0

0

0

|

Табл.1. АN

BN

у1

у2

& Табл.1. АN

BN

у1

у2

&

х1

х2

Мал. 9. Порт Мал. 10. х1

х2

Мал. 9. Порт Мал. 10. Порти та адаптори.

До інтерфейсних шин можуть підключатись різні пристрої зі своїми рівнями “0”та “1”, своїм форматом команд та данних та іншими особливостями. Для вирішення проблем узгодження периферійних пристроїв з шинами використовуються спеціальні пристрої, які називаються портами (ports). Вони виготовляються як окремі мікросхеми, або входять складовою частиною до мікропроцесорних комплектів. Обов’язковими елементами будь-якого порта є:

- дешифратор адреси;

- шинний підсилювач.

Дешифратор адреси призначений для дешифрації адресних сигналів та формування керуючих сигналів для ШП.

Реально зовнішні пристрої можуть мати різні форматикоманд та данних, працювати на своїх частотах синхронізації та інше. В таких випадках пристрій, який узгоджує роботу мікропроцесора та ЗП, повинен вирішувати задачі синхронізації та узгодження форматів данних. Частково ці функції може виконувати спеціальний буферний регістр послідоного типу. Вже при його наявності повинна формуваися відповідна послідовність взаємозв’язаних сигналів для запису данних в регістр, визначення, формування та створення необхідного формату, синхронізації, як з роботою зовнішнього пристрою, так і мікропроцесора. Все це в строгій послідовності повинно використовуватись як при передачі слова з ЗП в МП, так і навпаки. Фактично в розглядаємому випадку необхідне мікропрограмне керування, яке неможливо без мікропрограмного автомату.

Але всі ці перелічені операції не вирішують проблеми взаємоз’язку процесора з зовнішніми пристроями ще й тому, що повинна забезпечуватись синхронність передачі-прийому команд та данних. Для забезпечення асинхронного взаємозв’яку необхідно, щобмікропрграмний автомат зовнішнього пристрою міг звертатися до зовнішньої оперативної пам’яті за тими ж адресами, що і мікропроцесор. В такій структурі розглядаємий взаємообмін може виконуватись через узгоджені області адресного простору, в які процесор буде записувати результати обробки тієї інформації, яку зовнішній пристрій передав сюди раніше.

В такому разі мікропрграмний автомат перетворюється на мікропроцесор, який називається програмуємим периферійним адаптером (ППА).

Використовуються різні види взаємозв’язку між центральним процесором та ППА. В структурах мікропроцесорних систем з розглянутим раніше інтерфейсом ППА може звертатись до ОЗП по тим же шинам, що і центральний процесор. В такій ситуації повинна витримуватись необхідна взаємодія між процесором та ППА в використанні шин. Ця взаємодія полягає в тому, що ППА спеціальними сигналами запитує в ЦП дозволу на використання шин. Якщо ЦП дає дозвіл, то спеціальним сигналом він сповіщає про це ППА, а сам переходить на режим виконання внутрішніх команд. Відповідні порти переводяться в третій стан. Ситема сигналів, що приводить до тимчасового користувача шинами відноситься до категорії сигналів по “ЗАХВАТУ ШИН”. Режим роботи ППА з ОЗП називається режимом прямого доступу до пам’яті.

Система команд мікропроцесорів.

Самим низьким рівнем, який дозволяє описувати роботу цифрових пристроїв – це рівні логічних станів їх входів та виходів – таблиці станів.

Наступним рівнем є спосіб описання – це мова значень вхідних та вихідних сигналів, що складають мову мікрокоманд, та записуються 16-річними кодами.

Сукупність адресів та керуючих сигналів називаються мікрокомандою.

Третій рівень формалізації описання роботи мікропроцесора – це мова команд – тобто строга послідовність мікрокоианд, що записується в пам’яті МП.

Тобто, команда, це слово, або набір слів, які дешифруються ПК з допомогою ПЗП або ПЛМ в послідовність мікрокоманд. Звідси витікає, що будь-який процесор має строго фіксований і обмежений набір команд, який є характерним для данного процесора.

Будь-яка мікрокоманда характеризується своїм форматом. Під форматом мікрокоманди розуміється її протяжність та призначення кожного біта або їх групи.

Команди, також мають свій фіксований формат. (Протяжність мікрокоманди – це стандартна для данного процесора кількість біт в слові АЛП). В залежності від протяжності команди, вона може складатися з одного, двох, та трьох слів.

Формат пам’яті мікропоцесорної системи також тісно пов’язаний з довжиною слова. Тому при зберіганні таких команд відповідно використовується адресний простір та пам’ять. Якщо, наприклад, команда складається з трьох слів, а використовується з послідовною адресацією, то для зберігання такої команди використовуються три послідовні адреси. Для того, щоб таку команду вибрати з пам’яті, необхідно мати спеціальні засоби, щоб забезпечити її представлення в ПК як єдине ціле.

Структура команд повністю залежить від структури мікропроцесора, але незалежно від типу процесора прийнято вважати, що однослівні команди повністю складаютья з коду операції. Двослівні команди складаються з коду операції та однослівного операнда DN (N – кількість розрядів в слові). Трислівні команди також складаються з двох частин: перша частина – код операції, а друга – адреса, або двослівний операнд D2N.

Викортстовуємі типи команд тісно пов’язані з внутрішньою організацією та алгоритмом функціювання мікропрограмного автомата ПК процесора, та внутрішньою системою синхронізації.

МП система функціонує синхронно з частотою тактових сигналів зовнішнього генератора. В залежності від типу мікропроцесорів використовується одно- або двохфазна синхронізація. Незалежно від цього в мікропроцесорних системах використовуються більш тривалі інтервали часу, ніж тактовий інтервал зовнішнього генератора. Одним з таких інтервалів є машинний цикл – це інтервал, протягом якого МП звертається до пам’яті або пристрою вводу-виводу. Машинний цикл (МЦ) складає тільки частину циклу команди. На початку кожного МЦ на одному з виходів МП з’вляється сигнал синхронізації він передається по лінії шини керування в ОЗП або пристрої вводу-виводу і “сповіщає” про початок нового МЦ, в результаті чого досягається узгодження в часі зовнішніх пристроїв з роботою МП.

Цикл команди – це інтервал часу, необхідний для виборки з пам’яті команди, та її виконання. Він складається з 1-5 машинних циклів. Їх конкретне число залежить від складності операції, яка виконується в данній команді і дорівнює числу звернень МП до пам’яті. Тривалість виконання команди визначається кількістю тактів в циклі команди та тривалістю такту.

t

T 2T 3T 4T T 2T 3T T 2T

1й

МЦ 2й

МЦ 3й

МЦ 1й

МЦ 2й

МЦ 3й

МЦ

Цикл команди Цикл команди

Виборка команди Вик. ком.

Мал.11

Пртягом циклу команди, що ділиться на дві фази, робота МП виконується в такій послідовності. Пристрій керування задає початок чергового циклу шляхом формування сигналу, по якому число, що знаходиться в лічильнику команд, відправляється в буферний регістр адреси і через нього направляється в ЗП, де дешифрується. Після приходу від МП сигналу керування RD з елемента пам’яті, що знаходиться по вказаній адресі, зчитується слово команди, яке подається по шині данних в буферний регістр данних, а потім в пристрій керування, де дешифрується з допомогою кода операції. Ця послідовність операцій називається фазою виборки. За нею слідує виконавча фаза, в якій пристрій керування формує послідовність сигналів, необхідних для виконання команди. За цей час число, що знаходиться в лічильнику команд, збільшується на 1 і формується адреса команди, що стоїть слідом за виконуємою. Вона зберігається в лічильнику до приходу сигналу, що задає початок чергового циклу команди.

Окрім адреси елемента в якому зберігається необхідний байт від МП до ЗП поступає сигнал по шині керування, який визначає характер операції – запис, або зчитування. Виконання вказаних операцій проходить протягом інтервалу часу, що називається часом доступу. По закінченні цього інтервалу від ЗП в МП подається сигнал готовності, який є сигналом початку прийому, або, відповідно, передачі сигналів в ЗП. До одержання сигналу готовності МП знаходиться в стані очікування. Інтервал часу між імпульсами звернення до зовнішніх пристроїв та одержання від них відповіді називається циклом очікування.

Якщо, наприклад, цикл команди розглядати відповідно до команди вводу данних, то перші два машинних цикли будуть відноситись до фази виборки, а третій – до фази виконання команди. В усіх машинних циклах передається адреса, але в кожному циклі адреса належить своєму адресату, в першому – це адреса елемента, де здерігається код операції, в другому – адреса порта, що здерігає байт данних, в третьому – адреса акумулятора мікропроцесора, куди повинен поступити байт данних з порта.

|